Digi NS9750 User Manual

Page 233

w w w . d i g i e m b e d d e d . c o m

2 0 9

M e m o r y C o n t r o l l e r

The Dynamic Memory Control register controls dynamic memory operation. The

control bits can be changed during normal operation.

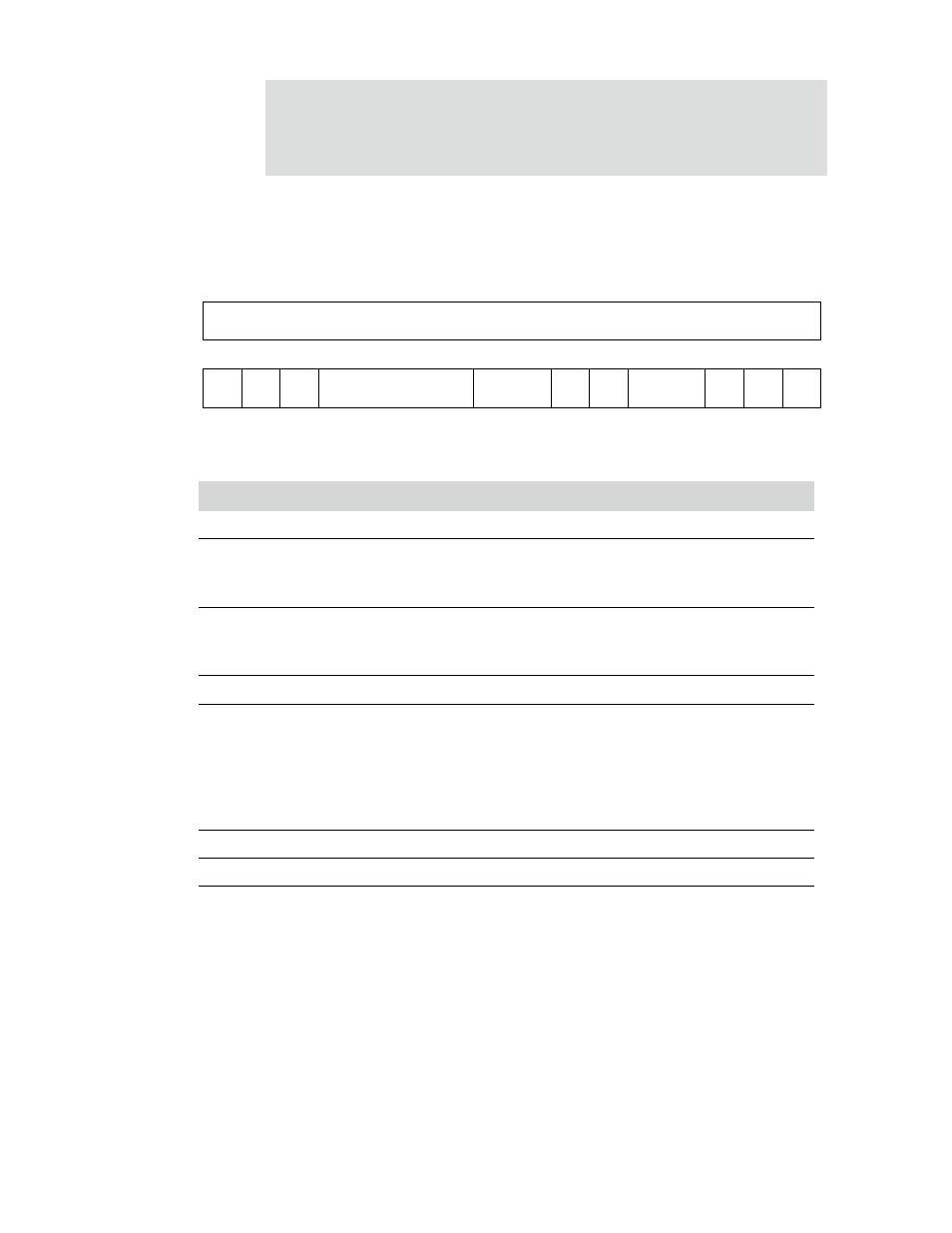

Register bit assignment

Bits

Access

Mnemonic

Description

D31:15

N/A

Reserved

N/A (do not modify)

D14

R/W

nRP

Sync/Flash reset/power down signal (

dy_pwr_n

)

0

dy_pwr_n

signal low (reset value on

reset_n

)

1

Set

dy_pwr_n

signal high

D13

R/W

Not used

Low-power SDRAM deep-sleep mode

0

Normal operation (reset value on

reset_n

)

1

Enter deep power down mode

D12:09

N/A

Reserved

N/A (do not modify)

D08:07

R/W

SDRAMInit

SDRAM initialization

00

Issue

SDRAM NORMAL

operation command (reset value on

reset_n

)

01

Issue

SDRAM MODE

command

10

Issue

SDRAM PALL

(precharge all) command

11

Issue

SDRAM NOP

(no operation) command

D06

N/A

Reserved

N/A (do not modify)

D05

R/W

Not used

Must write 0.

D04:03

N/A

Reserved

N/A (do not modify)

Table 141: Dynamic Memory Control register

CE

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

Reserved

SDRAMInit

Reserved

Rsvd

nRP

Not

used

Reserved

SR

Not

used

Rsvd

Not

used