Static ram sequential write cycles, Wtwr = 0, During a 32-bit transfer, all four – Digi NS9750 User Manual

Page 832: Signals will go low. during a 16-bit transfer, two, Signal will go low, Figure 116: static ram sequential write cycles, Wwen = 0

M e m o r y t i m i n g

8 0 8

N S 9 7 5 0 H a r d w a r e R e f e r e n c e

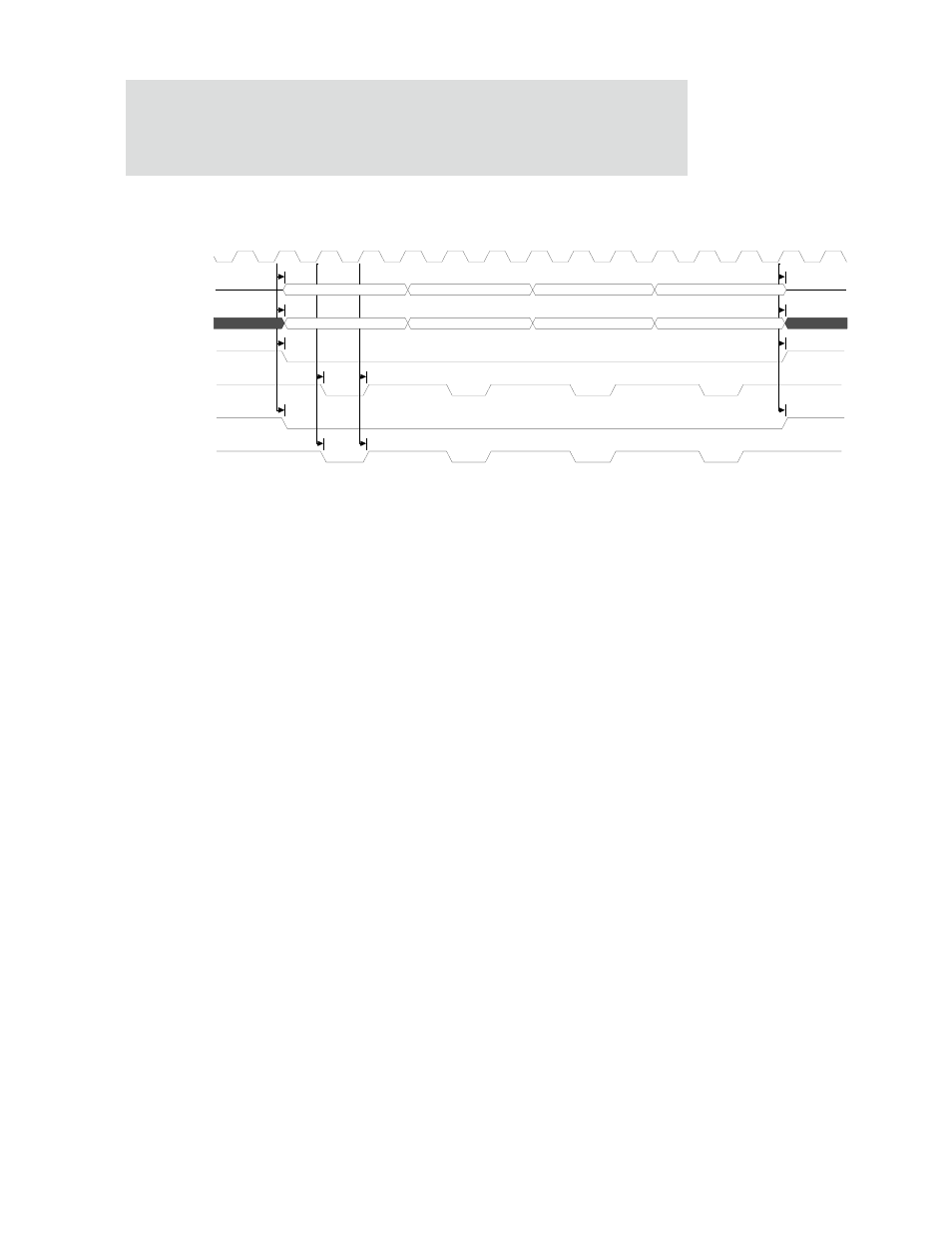

Static RAM sequential write cycles

Figure 116: Static RAM sequential write cycles

WTWR = 0

WWEN = 0

During a 32-bit transfer, all four

byte_lane

signals will go low.

During a 16-bit transfer, two

byte_lane

signals will go low.

During an 8-bit transfer, only one

byte_lane

signal will go low.

Note:

1

If the PB field is set to 0, the

byte_lane

signals will function as write enable signals and the

we_n

signal

will always be high.

M22

M21

M24

M23

M22

M21

M20

M19

M18

M17

M16

M15

Note1

CPU clock / 2

data<31:0>

addr<27:0>

st_cs_n<3:0>

we_n

byte_lane<3:0>

byte_lane[3:0] as WE*