Register bit assignment – Digi NS9750 User Manual

Page 412

E t h e r n e t C o n t r o l a n d S t a t u s r e g i s t e r s

3 8 8

N S 9 7 5 0 H a r d w a r e R e f e r e n c e

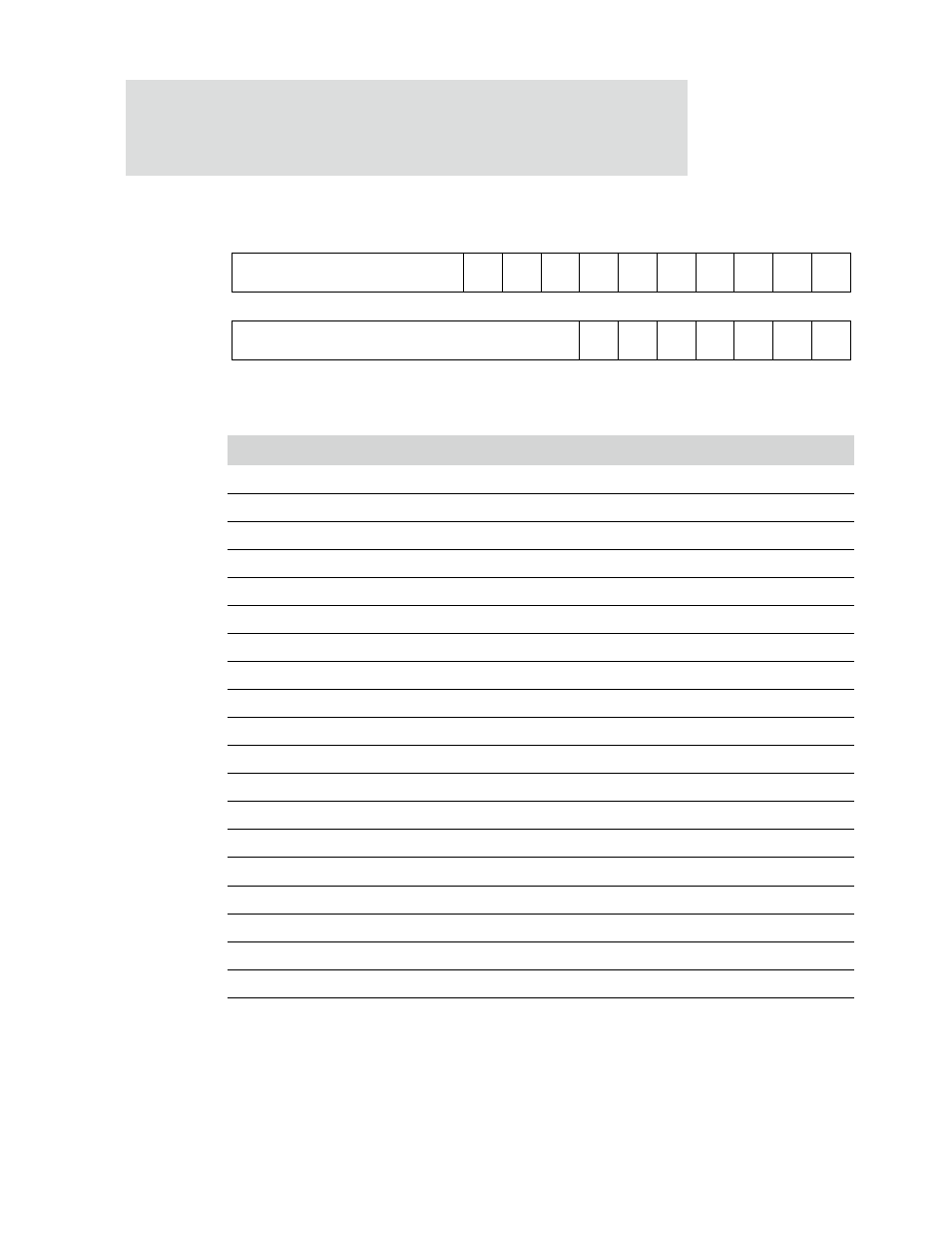

Register bit assignment

Bits

Access

Mnemonic

Reset

Description

D31:26

N/A

Reserved

N/A

N/A

D25

R/W

EN_RXOVFL_DATA

0

Enable the RXOVFL_DATA interrupt bit.

D24

R/W

EN_RXOVFL_STAT

0

Enable the RXOVFL_STATUS interrupt bit.

D23

R/W

EN_RXBUFC

0

Enable the RXBUFC interrupt bit.

D22

R/W

EN_RXDONEA

0

Enable the RXDONEA interrupt bit.

D21

R/W

EN_RXDONEB

0

Enable the RXDONEB interrupt bit.

D20

R/W

EN_RXDONEC

0

Enable the RXDONEC interrupt bit.

D19

R/W

EN_RXDONED

0

Enable the RXDONED interrupt bit.

D18

R/W

EN_RXNOBUF

0

Enable the RXNOBUF interrupt bit.

D17

R/W

EN_RXBUFFUL

0

Enable the RXBUFFUL interrupt bit.

D16

R/W

EN_RXBR

0

Enable the RXBR interrupt bit.

D15:07

N/A

Reserved

N/A

N/A

D06

R/W

EN_STOVFL

0

Enable the STOVFL interrupt bit.

D05

R/W

Not used

0

Always write as 0.

D04

R/W

EN_TXBUFC

0

Enable the TXBUFC interrupt bit.

D03

R/W

EN_TXBUFNR

0

Enable the TXBUFNR interrupt bit.

D02

R/W

EN_TXDONE

0

Enable the TXDONE interrupt bit.

D01

R/W

EN_TXERR

0

Enable the TXERR interrupt bit.

D00

R/W

EN_TXIDLE

0

Enable the TXIDLE interrupt bit.

Table 241: Ethernet Interrupt Enable register

Reserved

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

Reserved

EN_RX

DONE

C

EN_RX

DONE

D

EN_

RXNO

BUF

EN_RX

BUF

FUL

EN_

RXBR

EN_RX

OVFL_

DATA

EN_RX

OVFL_

STAT

EN_

RX

BUFC

EN_RX

DONE

A

EN_RX

DONE

B

EN_ST

OVFL

Not

used

EN_TX

BUFC

EN_TX

BUF

NR

EN_

TX

DONE

EN_

TX

ERR

EN_

TX

IDLE