Digi NS9750 User Manual

Page 212

D y n a m i c m e m o r y c o n t r o l l e r

1 8 8

N S 9 7 5 0 H a r d w a r e R e f e r e n c e

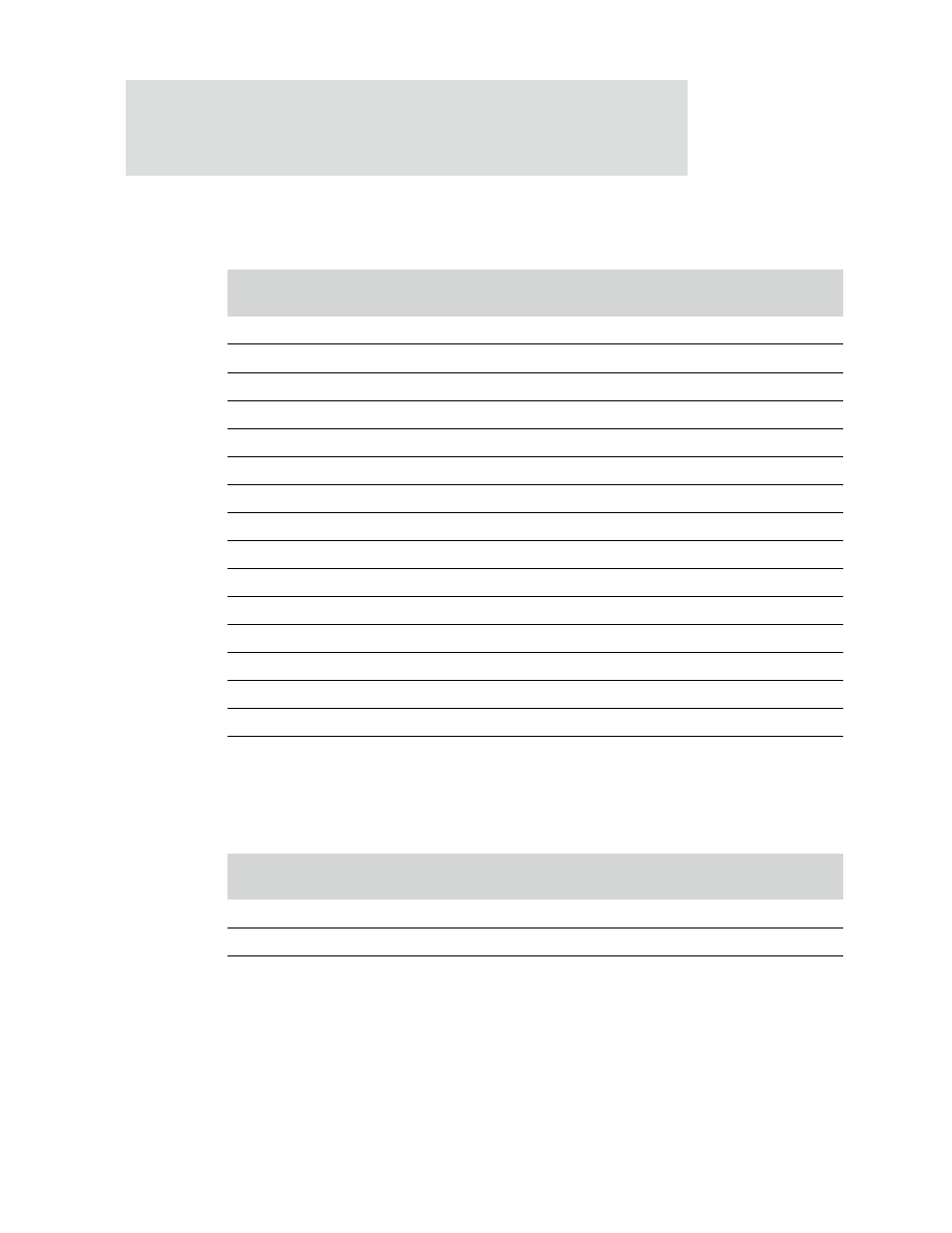

Table 120 shows the outputs from the memory controller and the corresponding

inputs to the 64M SDRAM (8Mx8, pins 13 and 14 used as bank selects).

Table 121 shows the outputs from the memory controller and the corresponding

inputs tot he 128M SDRAM (8Mx16, pins 13 and 14 used as bank selects).

Output address

(

ADDROUT

)

Memory device

connections

AHB address to row

address

AHB address to

column address

14

BA1

11

11

13

BA0

10

10

12

-

-

-

11

11

23

-

10

10/AP

22

AP

9

9

21

-

8

8

20

9

7

7

19

8

6

6

18

7

5

5

17

6

4

4

16

5

3

3

15

4

2

2

14

3

1

1

13

2

0

0

12

**

Table 120: Address mapping for 64M SDRAM (8Mx8, RBC)

Output address

(

ADDROUT

)

Memory device

connections

AHB address to row

address

AHB address to

column address

14

BA1

11

11

13

BA0

10

10

12

-

-

-

Table 121: Address mapping for 128M SDRAM (8Mx16, RBC)