Input high, as shown in figure 70, For 100 mbps) or, Must be valid by the 254 – Digi NS9750 User Manual

Page 360: Di-bit of data (the first di-bit is 0, Di-bit), Figure 69: rmii phy receive interface

E x t e r n a l C A M f i l t e r i n g

3 3 6

N S 9 7 5 0 H a r d w a r e R e f e r e n c e

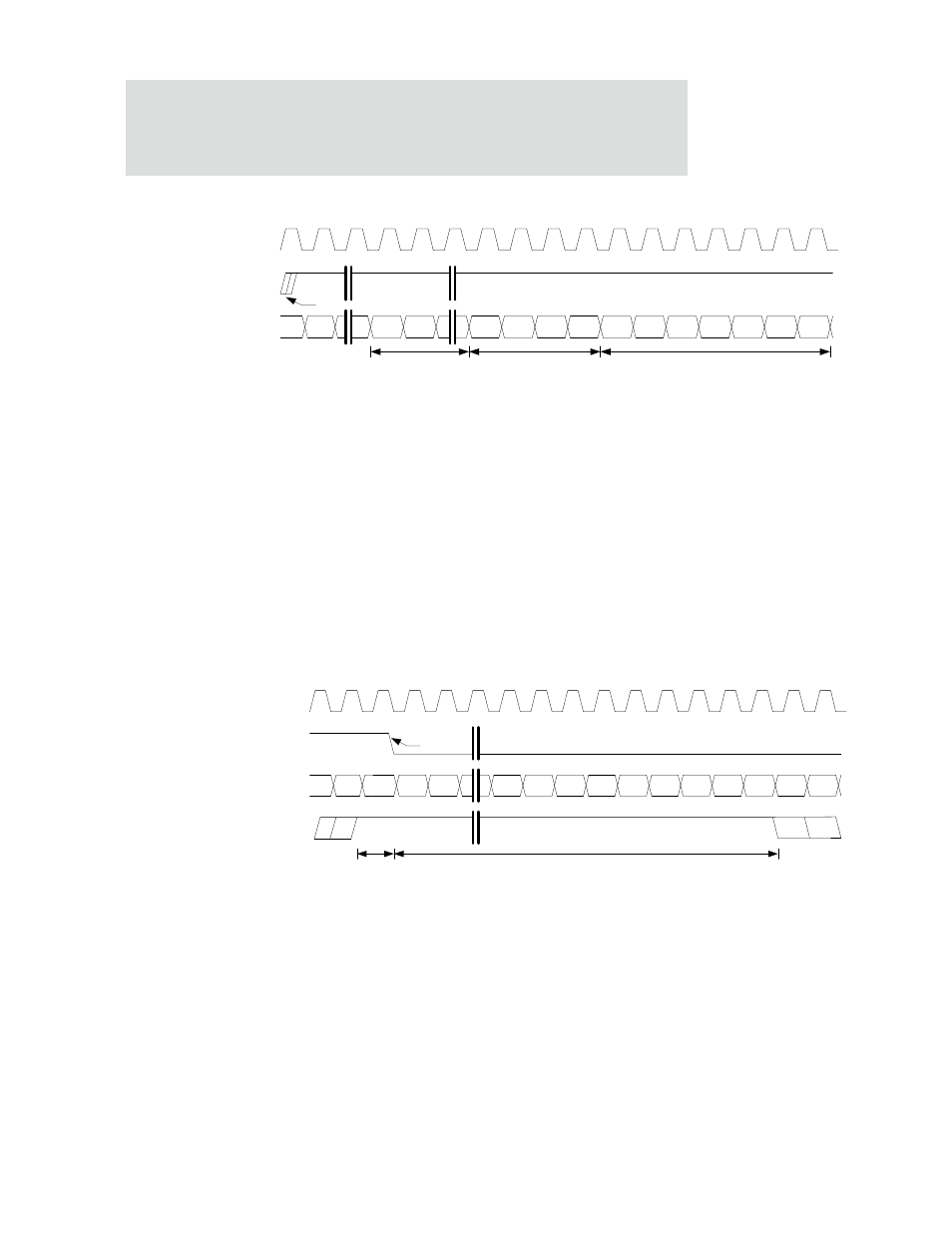

Figure 69: RMII PHY receive interface

After performing the necessary destination address lookup, the incoming frame can

be rejected by the CAM filtering hardware by asserting the

CAM_REJECT(GPIO[20])

input

high, as shown in Figure 70.

CAM_REJECT(GPIO[20])

must be asserted no later than one

di-bit nibble before the end of the frame (that is, when

CRS_DV

is negated). Once the

signal is asserted, it must remain asserted until

16 REF_CLKs

(for 100 Mbps) or

128

REF_CLKS

(for 10 Mbps) after the end of the frame, to guarantee that the

RX_WR

logic

has captured it. For example, a 64-byte frame contains 256 di-bits (that is, 2 bits) of

data on the RMII interface.

CAM_REJECT

must be valid by the 254

th

di-bit of data (the

first di-bit is 0

th

di-bit).

Figure 70: External Ethernet CAM filtering for RMII PHY

00

01

01

01

01

11

10

00

11

11

Preamble

REF_CLK

RXD[1:0]

00

00

01

01

01

10

11

CRS_DV

SFD

Packet Data

Note 1

1. Rising edge of CRS_DV asynchronous relative to REF_CLK

2. CRS_DV synchronous to REF_CLK once RXD[1:0] changes from "00"

to "01" at start of preamble.

11

00

00

00

00

00

00

00

00

00

REF_CLK

RXD[1:0]

01

10

00

00

00

00

00

CRS_DV

Note 1

1. Falling edge of CRS_DV synchronous relative to REF_CLK.

CAM_REJECT

REJECT setup to end of Packet

(1 REF_CLK min)

REJECT hold from end of packet

(16/128 REF_CLKs min for 100/10Mbps)