Ns9750, System-level interfaces – Digi NS9750 User Manual

Page 32

S y s t e m - l e v e l i n t e r f a c e s

8

N S 9 7 5 0 H a r d w a r e R e f e r e n c e

System-level interfaces

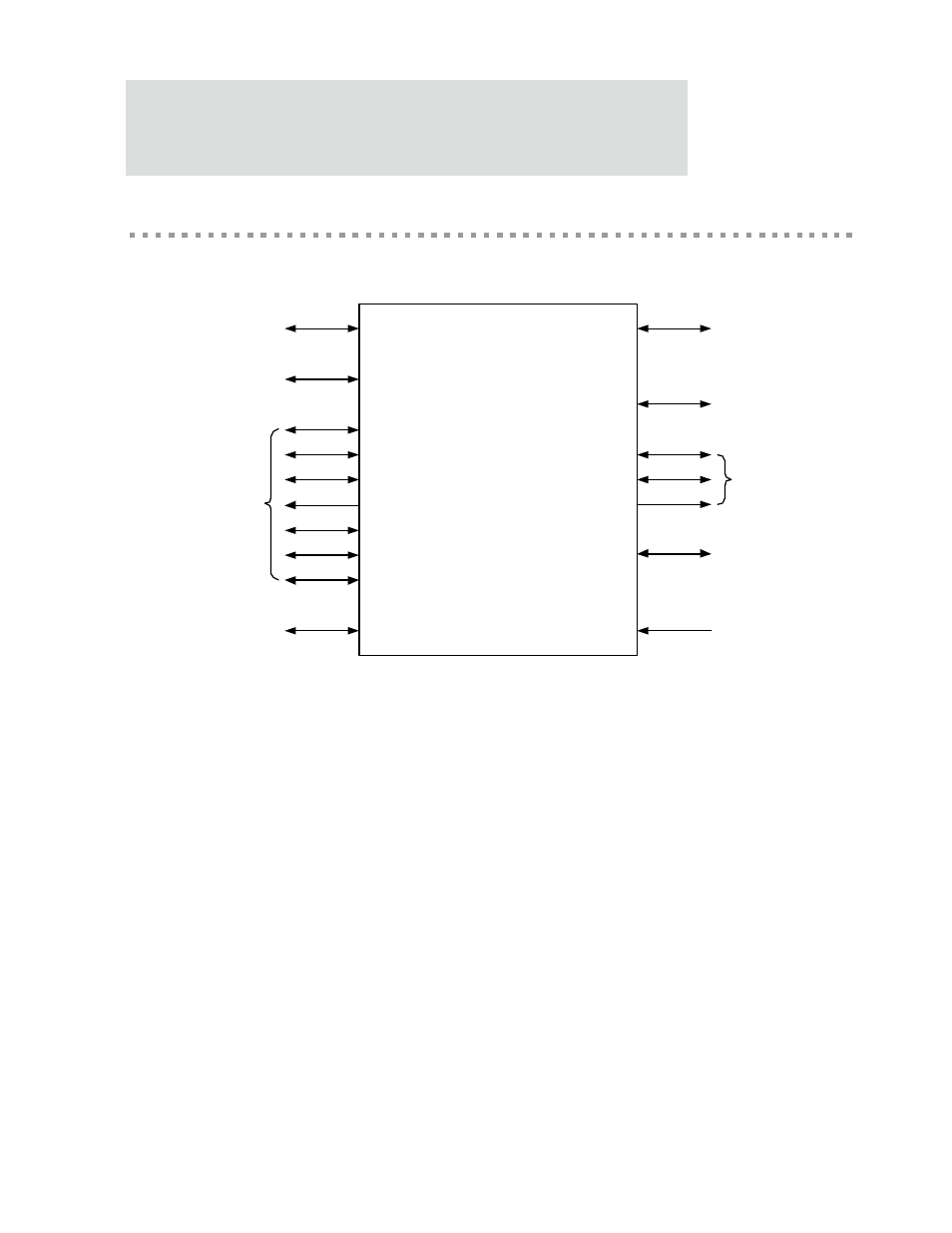

Figure 1 shows the NS9750 system-level interfaces.

Figure 1: System-level hardware interfaces

Ethernet MII/RMII interface to external PHY

System memory interface

–

Glueless connection to SDRAM

–

Glueless connection to buffered PC100 DIMM

–

Glueless connection to SRAM

–

Glueless connection to Flash memory or ROM

PCI muxed with CardBus interface

USB host or device interface

I

2

C interface

50 GPIO pins muxed with:

–

Four 8-pin-each serial ports, each programmable to UART or SPI

NS9750

I

2

C

Clocks & Reset

JTAG

Ethernet

Controls

Data

Address

PCI/CardBus

Power & Ground

GPIO

Sy stem

Memory

USB Host or Dev ice

Serial

1284

LCD

Ext. DMA

Ext. IRQ

Timers/Counters

USB Host control