Digi NS9750 User Manual

Page 45

w w w . d i g i e m b e d d e d . c o m

2 1

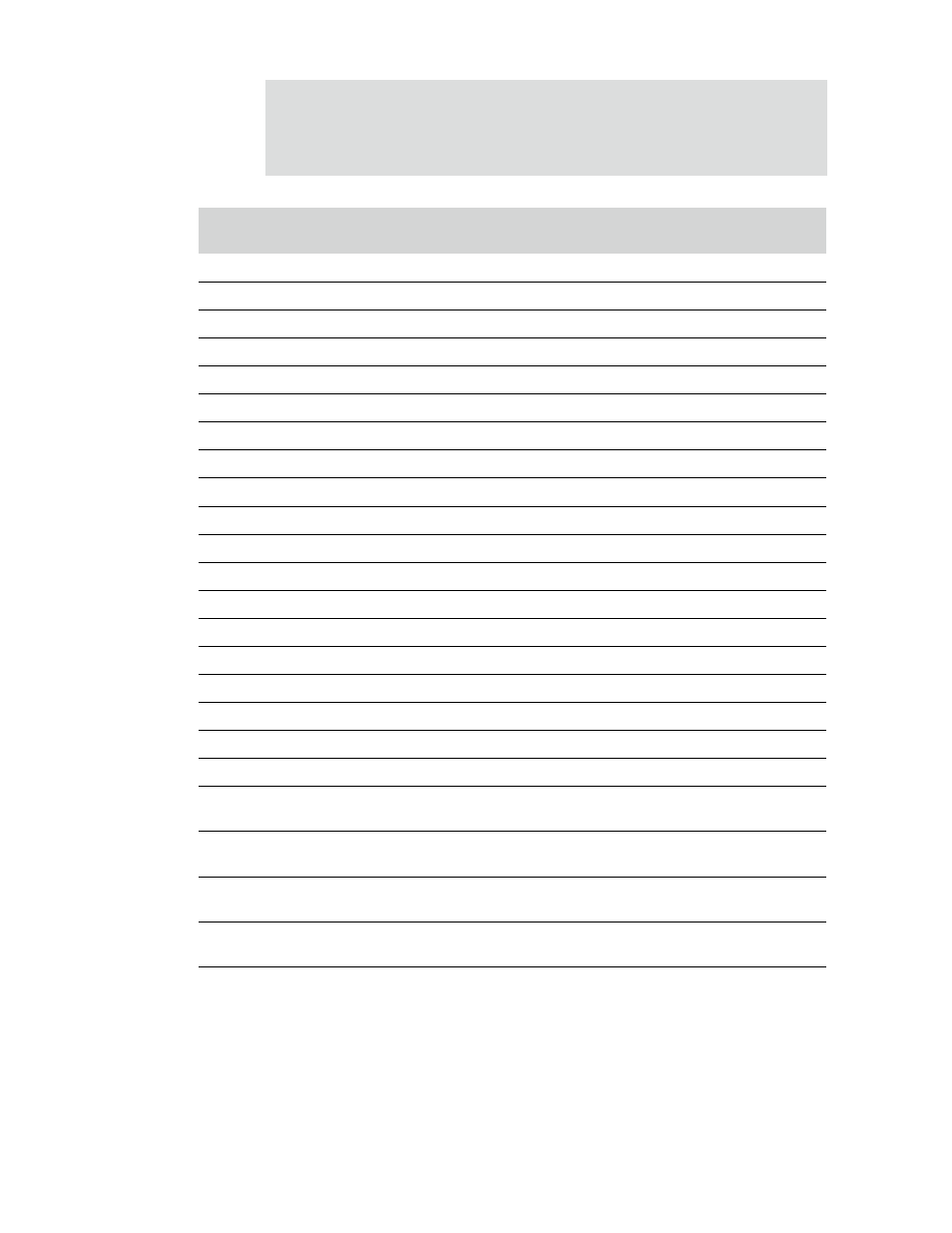

N S 9 7 5 0 P i n o u t

A25

data[21]

8

I/O

Data bus signal

C22

data[22]

8

I/O

Data bus signal

D21

data[23]

8

I/O

Data bus signal

B23

data[24]

8

I/O

Data bus signal

A24

data[25]

8

I/O

Data bus signal

A23

data[26]

8

I/O

Data bus signal

B22

data[27]

8

I/O

Data bus signal

C21

data[28]

8

I/O

Data bus signal

A22

data[29]

8

I/O

Data bus signal

B21

data[30]

8

I/O

Data bus signal

C20

data[31]

8

I/O

Data bus signal

E1

data_mask[0]

8

O

SDRAM data mask signal

F2

data_mask[1]

8

O

SDRAM data mask signal

G3

data_mask[2]

8

O

SDRAM data mask signal

F1

data_mask[3]

8

O

SDRAM data mask signal

C5

clk_in[0]

I

SDRAM feedback clock. Connect to clk_out[0].

D2

clk_in[1]

I

Connect to GND

E3

clk_in[2]

I

Connect to GND

E2

clk_in[3]

I

Connect to GND

B4

byte_lane_sel_n[0]

8

O

Static memory byte_lane_enable[0] or

write_enable_n[0] for byte-wide device signals

F4

byte_lane_sel_n[1]

8

O

Static memory byte_lane_enable[1] or

write_enable_n[1] for byte-wide device signals

D1

byte_lane_sel_n[2]

8

O

Static memory byte_lane_enable[2] or

write_enable_n[2] for byte-wide device signals

F3

byte_lane_sel_n[3]

8

O

Static memory byte_lane_enable[3] or

write_enable_n[3] for byte-wide device signals

B5

cas_n

8

O

SDRAM column address strobe

Pin #

Signal Name

U/D

OD

(mA)

I/O

Description

Table 3: System Memory interface pinout