Digi NS9750 User Manual

Page 524

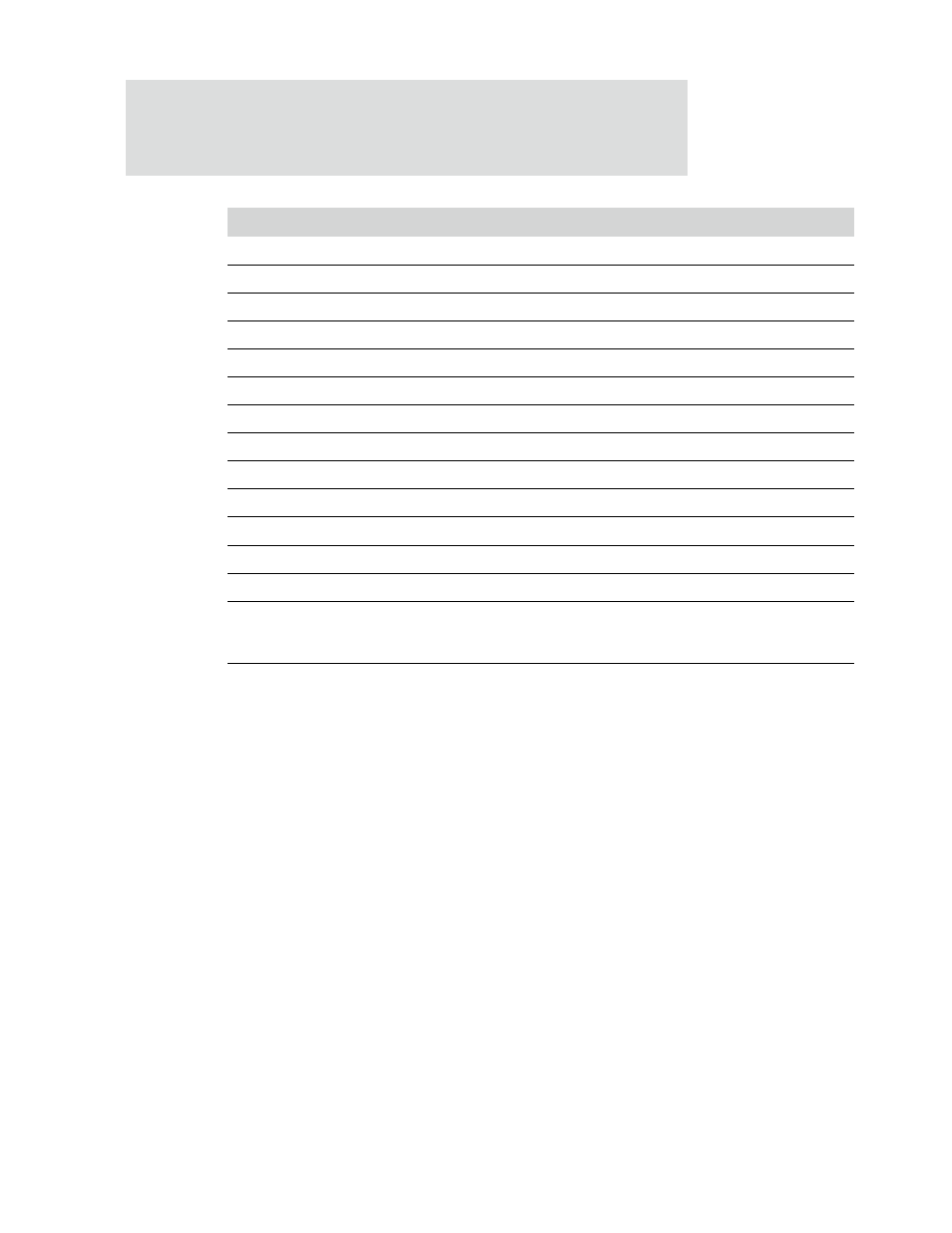

B B u s B r i d g e C o n t r o l a n d S t a t u s r e g i s t e r s

5 0 0

N S 9 7 5 0 H a r d w a r e R e f e r e n c e

D23:13

R/W

Not used

0x000

Always set this field to 0.

D12

R/W

Not used

0

Always write to 0.

D11

R/W

1284E

0

Enable interrupt from IEEE-1284 module.

D10

R/W

I2CE

0

Enable interrupt from I2C module.

D09

R/W

SDTXE

0

Enable interrupt from SER transmit module D.

D08

R/W

SDRXE

0

Enable interrupt from SER receive module D.

D07

R/W

SCTXE

0

Enable interrupt from SER transmit module C.

D06

R/W

SCRXE

0

Enable interrupt from SER receive module C.

D05

R/W

SATXE

0

Enable interrupt from SER transmit module A.

D04

R/W

SARXE

0

Enable interrupt from SER receive module A.

D03

R/W

SBTXE

0

Enable interrupt from SER transmit module B.

D02

R/W

SBRXE

0

Enable interrupt from SER receive module B.

D01

R/W

USBE

0

Enable interrupt from USB module.

D00

R/W

DMAE

0

Enable aggregate interrupt from BBus DMA module.

These interrupts can be controlled on a per-DMA channel

basis in the BBus utility module.

Bits

Access

Mnemonic

Reset

Description

Table 301: BBus Bridge Interrupt Enable register bit definition