Agu bit mask instructions (bmu) -50 – Freescale Semiconductor StarCore SC140 User Manual

Page 82

2-50

SC140 DSP Core Reference Manual

Address Generation Unit

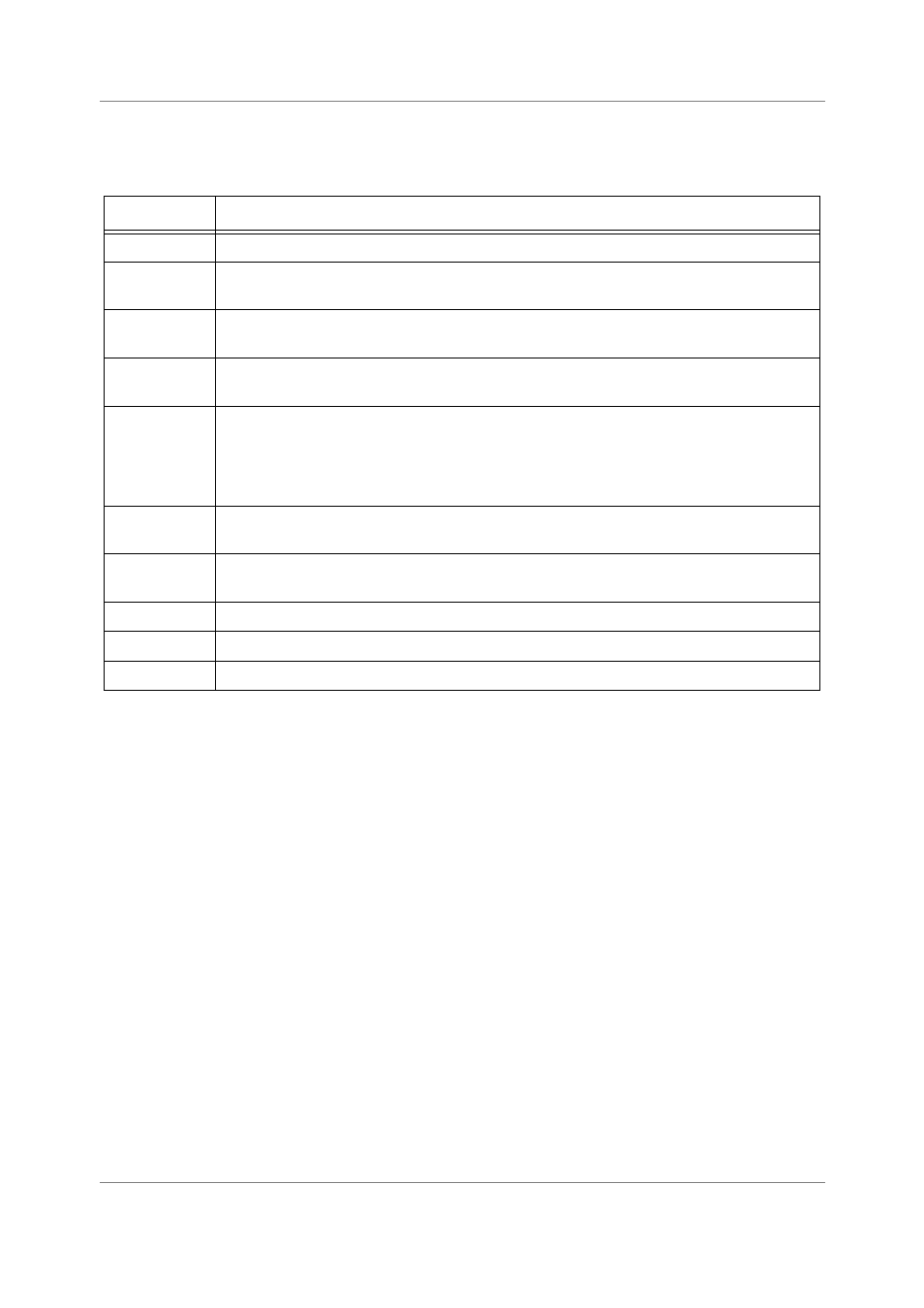

Table 2-24 lists the arithmetic instructions that are executed in the BMU.

2.3.6.1 Bit Mask Test and Set (Semaphore Support) Instruction

The bit mask test and set instruction (BMTSET) provides support for hardware semaphores. A semaphore

is a signal which can be set to indicate whether a program resource can be accessed or not. The destination

of this instruction can be a register or a memory location in either internal or external memory. If the

semaphore indicates that the resource is available, the T bit has the value 0. If the semaphore indicates that

the resource is not available (T = 1), a jump can be made to skip the resource code.

This instruction performs the following tasks:

1. Reads the destination register, tests the data, and sets the T bit, if every bit that has the value

1 in the mask is 1 in the destination.

2. Writes back to the destination a word with ones for the masked bits, and the original

destination bits for the unmasked bits.

3. Sets the T bit if the set (write) failed.

Normally, the BMTSET consists of three indivisible operations: read, update the T bit, and

write. A set (write) failed condition occurs if the destination failed to be written indivisibly

from the previous read operation of that BMTSET instruction. The memory subsystem

signals the core of a write failure if a memory access that is initiated by another master

source intervenes between the read and the write accesses of the BMTSET operation. As a

result of the non-exclusive write indication, the T bit is set, signalling that the resource may

not be available, thereby avoiding a hazard condition.

Table 2-24. AGU Bit Mask Instructions (BMU)

Instruction

Description

AND.W

Logical AND on a 16-bit operand

BMCHG

Bit mask change

Inverts every bit in the destination (register or memory) that has the value 1 in the mask.

BMCLR

Bit mask clear

Clears every bit in the destination (register or memory) that has the value 1 in the mask.

BMSET

Bit mask set

Sets every bit position in the destination (register or memory) that has the value 1 in the mask.

BMTSET

Bit mask test (if set) and set

Sets the T bit if every bit that has the value 1 in the mask is 1 in the destination (register or

memory). Sets (writes) every bit in the destination (register or memory) that has the value 1 in

the mask, and sets the T-bit if the set (write) failed. See

Section 2.3.6.1, “Bit Mask Test and Set

(Semaphore Support) Instruction.”

BMTSTC

Bit mask test if clear

Sets the T-bit, if every bit position that has the value 1 in the mask is 0 in an operand.

BMTSTS

Bit mask test if set

Sets the T bit if every bit position that has the value 1 in the mask is 1 in an operand.

EOR.W

Logical exclusive OR on a 16-bit operand

NOT.W

Binary inversion of a 16-bit operand

OR.W

Logical OR on a 16-bit operand