6 bit mask instructions, Bit mask instructions -49 – Freescale Semiconductor StarCore SC140 User Manual

Page 81

Address Generation Unit

SC140 DSP Core Reference Manual

2-49

2.3.6 Bit Mask Instructions

The SC140 core provides bit mask instructions on all address registers (R0–R15), all DALU registers

(D0–D15), all control registers (EMR, VBA, SR, MCTL), and all memory locations.

Bit mask instructions provide an easy way of setting, clearing, inverting, or testing a selected but not

necessarily adjacent group of bits in a register or memory location.

All bit mask instructions work on 16-bit data. This data can be the contents of a memory location or a

portion (high or low) of a register.

Only a single bit mask instruction is allowed in one execution set since only one execution unit exists for

these instructions. A subgroup of the bit mask instructions (BMTSET) supports hardware semaphores. For

more information, see

Section 2.3.6.1, “Bit Mask Test and Set (Semaphore Support) Instruction.”

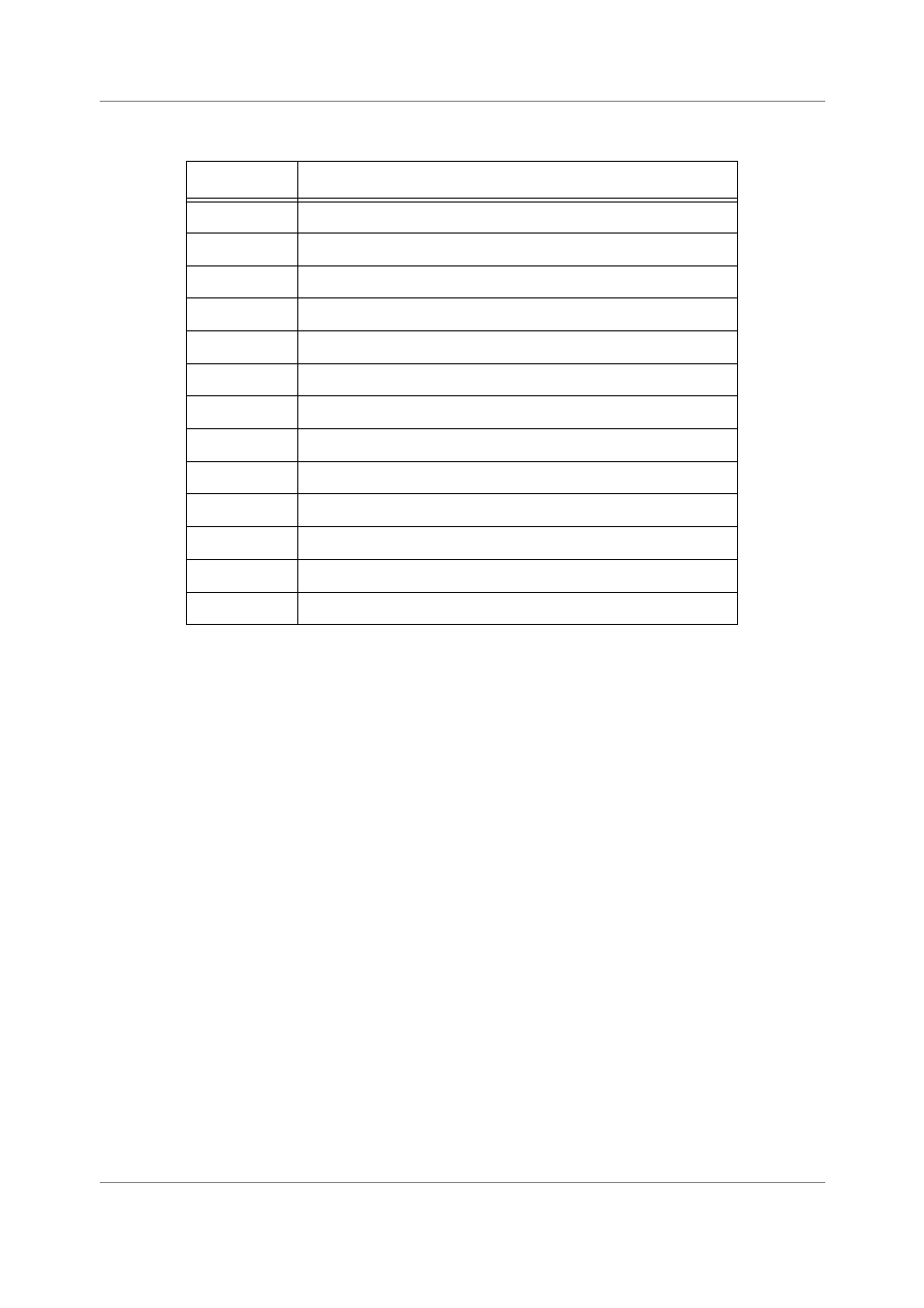

DECGEA

AGU Decrement and set T if result is equal to or greater than zero

INCA

AGU Increment register (affected by the modifier mode)

LSRA

AGU Logical shift right (32-bit)

SUBA

AGU Subtract (affected by the modifier mode)

SXTA.B

AGU Sign-extend byte

SXTA.W

AGU Sign-extend word

TFRA

AGU Register transfer

TSTEQA

AGU Test for equal to zero

TSTEQA.W

AGU Test for equal to zero on lower 16 bits

TSTGEA

AGU Test for greater than or equal to zero

TSTGTA

AGU Test for greater than zero

ZXTA.B

AGU Zero-extend byte

ZXTA.W

AGU Zero-extend word

Table 2-23. AGU Arithmetic Instructions (Continued)

Instruction

Description