Instruction formats and opcodes, Instruction fields – Freescale Semiconductor StarCore SC140 User Manual

Page 614

A-300

SC140 DSP Core Reference Manual

MOVES.4F

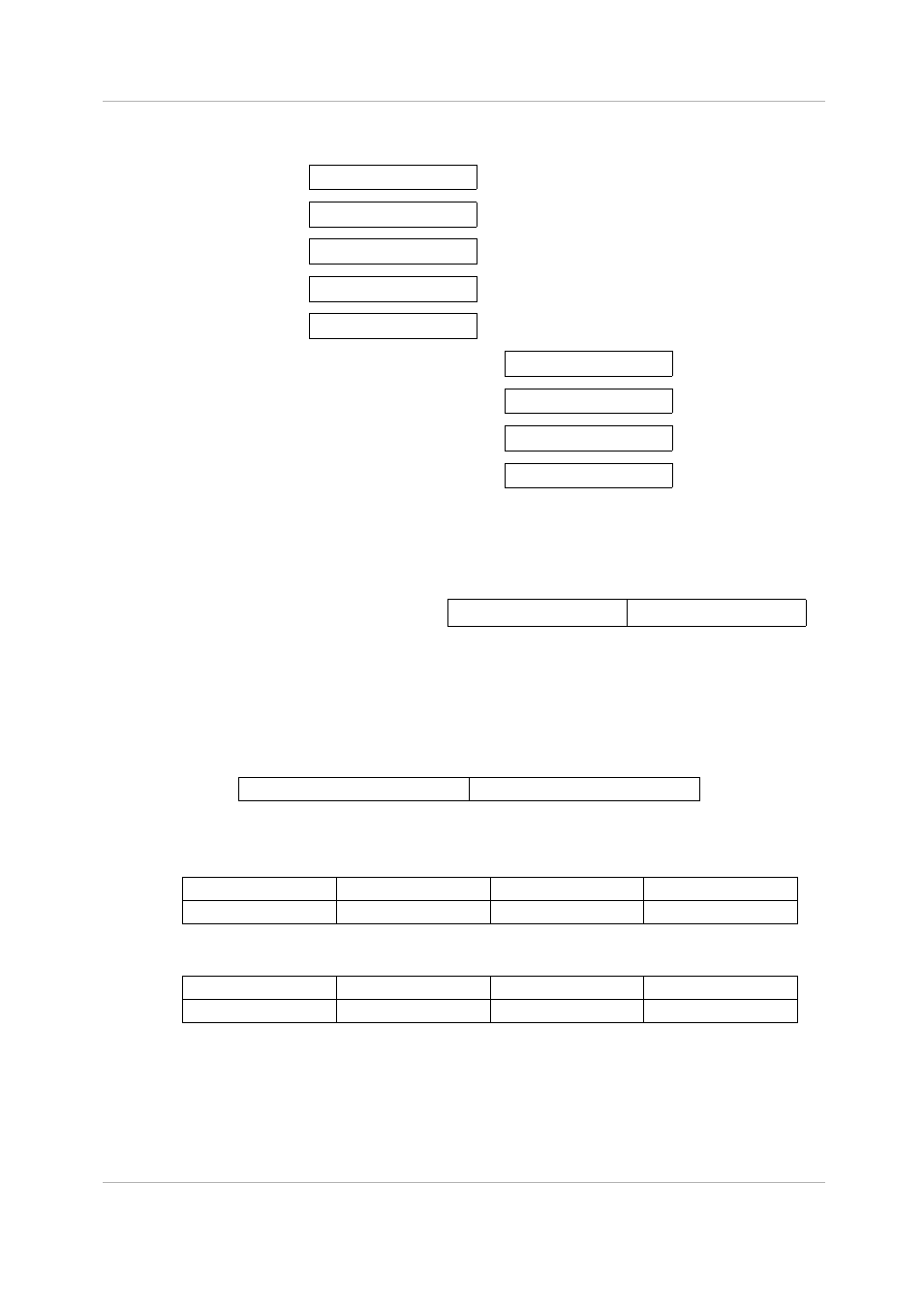

Instruction Formats and Opcodes

Notes:

1.

** indicates serial grouping encoding.

2.

When the form (Rn + N0) is used in EA, the cycle count is increased by 1.

Instruction Fields

Da:Db:Dc:Dd

k

Data Register Quad

EA

MMM

Effective Address Notation

Rn

RRR

Address Register

R0

$0000 0050

L0:D0

$1:$0 08000 0000

L1:D1

$0:$00 7FFF FFFF

L2:D2

$1:$87 6543 2100

L3:D3

$0:$FF 8765 4321

$0050

$7FFF

$0052

$7FFF

$0054

$8000

$0056

$8765

Instruction

Words Cycles Type

Opcode

15

8

7

0

MOVES.4F

1

1

2

1

0

*

0

0

1

k

0

0

1

1 M M M R R R

Da:Db:Dc:Dd,(EA)

0

D0:D1:D2:D3

1

D4:D5:D6:D7

Note:

This instruction can specify D8-D15 as operands by using a prefix.

000

(Rn+N0)

010

(Rn)

100

(Rn)+N0

110

(Rn)+N2

001

(Rn)–

011

(Rn)+

101

(Rn)+N1

111

(Rn)+N3

000

R0

010

R2

100

R4

110

R6

001

R1

011

R3

101

R5

111

R7

Note:

This instruction can specify R8-R15 as operands by using a high register prefix.

Register/Memory Address

Before

After