Example, Instruction formats and opcodes instruction fields – Freescale Semiconductor StarCore SC140 User Manual

Page 387

BMCHG.W

SC140 DSP Core Reference Manual

A-73

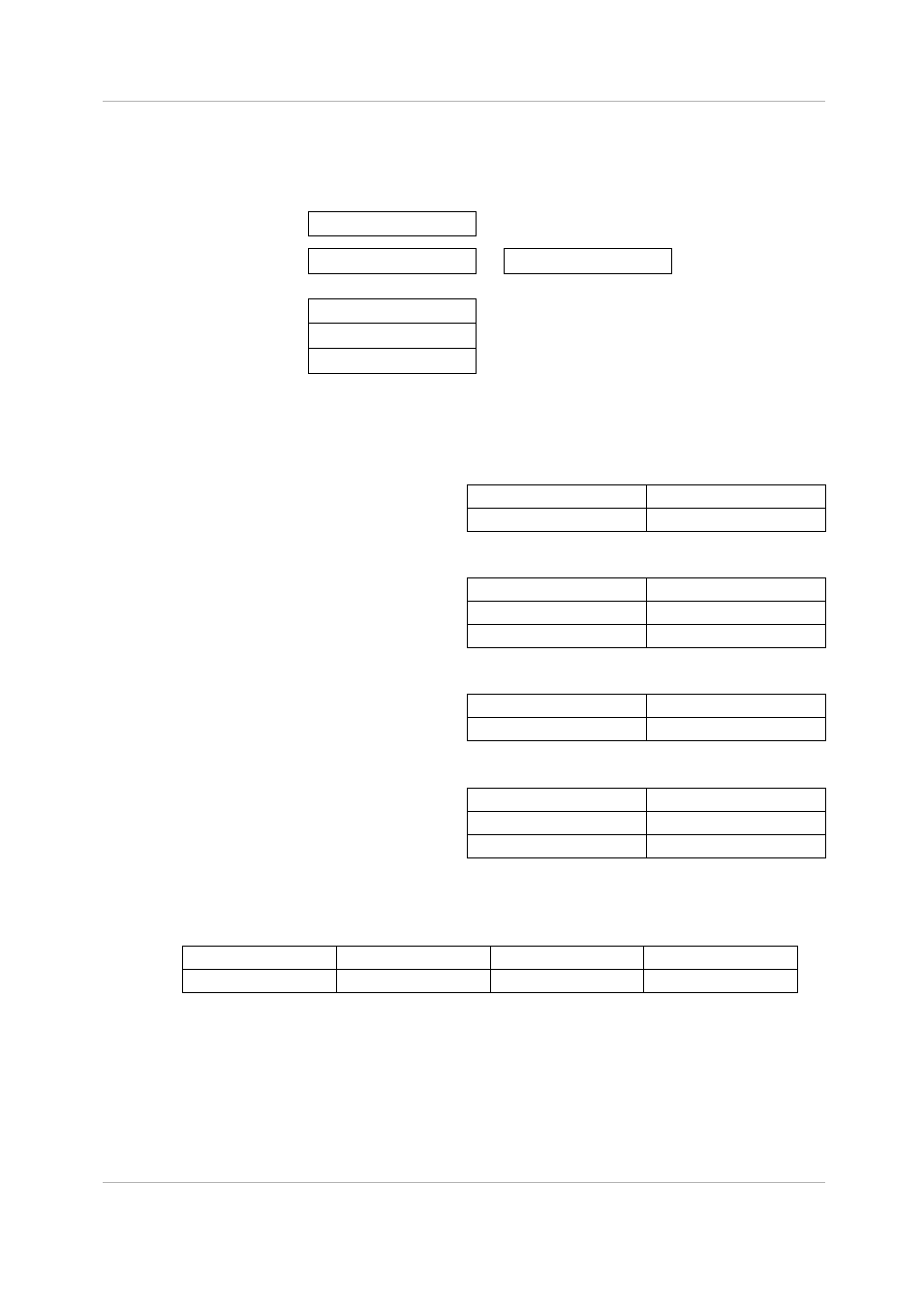

Example

bmchg.w #$661f,<$800c

Instruction Formats and Opcodes

Instruction Fields

Rn

RRR

Address Register

Register/Memory Address

Before

After

immediate

$661F

$800C

$ACE1

$CAFE

In binary, $661F

0110

0110

0001

1111

$ACE1

1010

1100

1110

0001

$CAFE

1100

1010

1111

1110

Instruction

Words Cycles Type

Opcode

15

8

7

0

BMCHG.W #u16,(SP–u5)

2

3

3

0

0

0

0

0

0

1

0

i

i

i

A

A

A

A

A

1

0

1

i

i

i

i

i

i

i

i

i

i

i

i

i

15

8

7

0

BMCHG.W #u16,(SP+s16)

3

3

3

0

0

1

1

1

0

1

0

A

A

A

i

i

0

1

1

0

0

1

A

A

A

A

A

A

A

A

A

A

A

A

A

1

0

i

i

i

i

i

i

i

i

i

i

i

i

i

i

15

8

7

0

BMCHG.W #u16,(Rn)

2

2

3

0

0

0

1

0

0

1

0

i

i

i

0

1

R R R

1

0

1

i

i

i

i

i

i

i

i

i

i

i

i

i

15

8

7

0

BMCHG.W #u16,(a16)

3

2

3

0

0

1

1

1

0

1

0

A

A

A

i

i

0

0

1

0

0

1

A

A

A

A

A

A

A

A

A

A

A

A

A

1

0

i

i

i

i

i

i

i

i

i

i

i

i

i

i

000

R0

010

R2

100

R4

110

R6

001

R1

011

R3

101

R5

111

R7

Note:

This instruction can specify R8-R15 as operands by using a high register prefix.

a16

AAAAAAAAAAAAAAAA

16-bit unsigned absolute address

#u16

iiiiiiiiiiiiiiii

16-bit unsigned immediate data

u5

AAAAA0

5-bit unsigned SP address offset