Event selector mask debug state (esel_dm) -63 – Freescale Semiconductor StarCore SC140 User Manual

Page 173

Event Selector (ES) Registers

SC140 DSP Core Reference Manual

4-63

For each outcome, the individual events could be AND-ed or OR-ed as specified in ESEL_CTRL. When

the ESEL_CTRL is configured as “OR” for a certain outcome, all events could be enabled as needed.

However, AND-ing events is more restricted, since the respective events that are AND-ed have to be

related so that the combination will be meaningful. For example, there is no meaning to AND an EE pin

assertion (a transient event) with an EDCA event because there is no practical way to synchronize them.

Combining events with an AND condition in the ESEL_CTRL register is allowed only for the following

options:

— EDCA0-5 events all configured to detect a PC

meaning: the events relate to the same execution set

— One EDCA0-5 event configured to detect data accesses with an EDCD event

meaning: a matching address-data pair of the same access.

The interface for the optional external EDCA6 and EDCA7 has the same timing as data address events.

This means that if the external EDCAs were implemented with the same detection timing as the internal

ones, they could be used in the event selector with other events in same way as the internal EDCAs.

In general, the options for combining external EDCA events in the event selector are as follows:

— OR-ed with other EOnCE events, as asynchronous events with respect to core activity.

— AND-ed with other EOnCE events, if used as an enabling event that is asserted continuously for

extended periods. In this case the assertion and de-assertion transitions of EDCA6/7 events

should be controlled by the system (in SW or HW) since the transition edge cases could be

problematic to detect.

— AND-ed with an EDCD event, intended to detect an address/data pair on the same bus.

In case the event selector is configured to have some events cause entry into debug state and other events

to cause a debug exception (ESEL_DM and ESEL_DI are both enabled at the same time), then the events

configured in each of them cannot be with an AND condition in ESEL_CTRL.

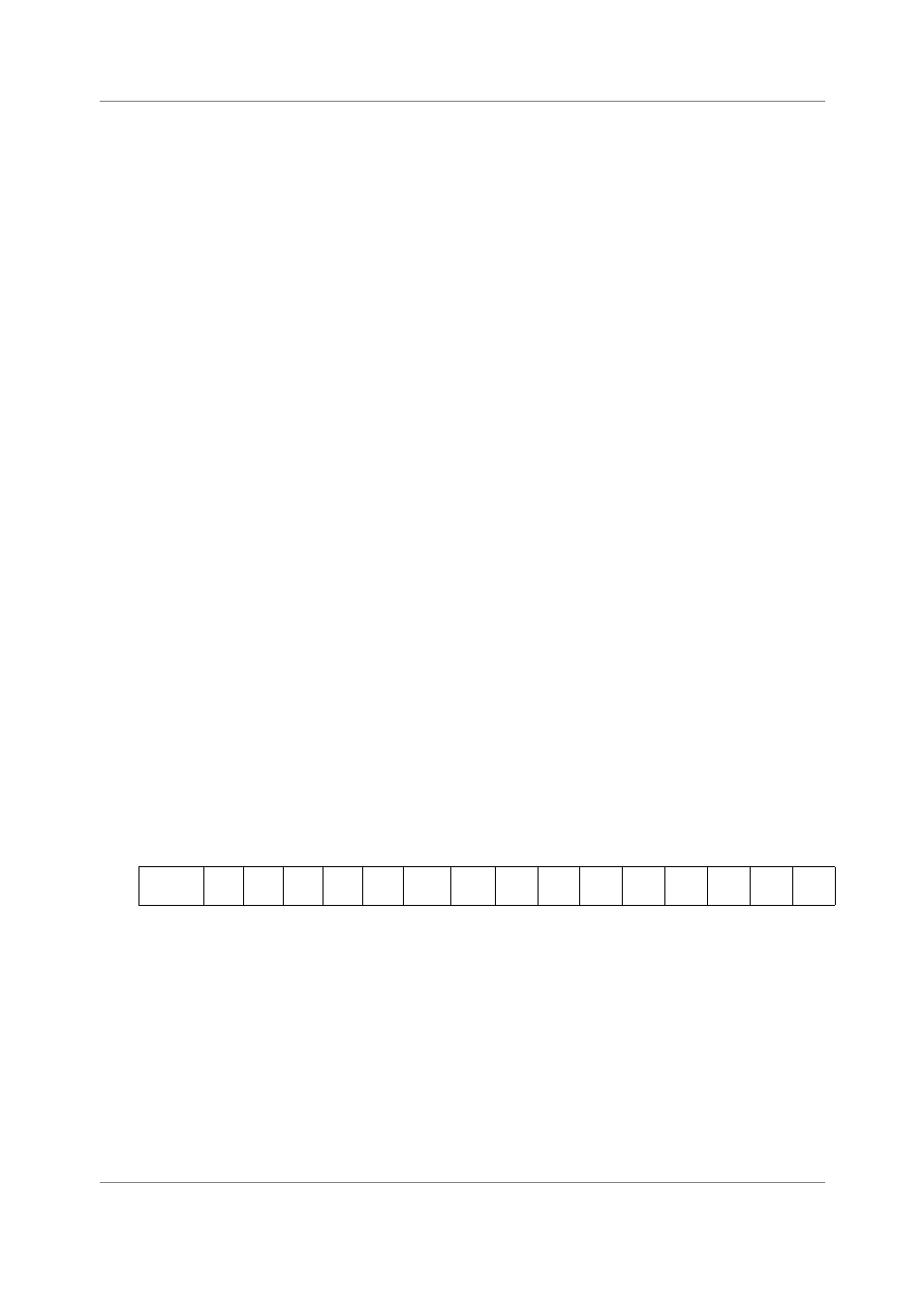

4.10.2 Event Selector Mask Debug State Register (ESEL_DM)

This 16-bit register has one bit for each source of event selection. Setting the appropriate bit configures the

related source to cause entry into debug state.

Figure 4-24 displays the bit configuration of ESEL_DM.

Figure 4-24. Event Selector Mask Debug State (ESEL_DM)

If multiple sources are configured to cause entry into debug state, they are ANDed or ORed according to

the value of the SELDM bit in the ESEL_CTRL. For more information, see

Selector Control Register (ESEL_CTRL),”

on page 4-61. If all the bits are set to zero, the ES does not

enter debug state.

BIT 15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

BIT 0

DEBUGE

V

EE4

EE3

EE2

EE1

EE0

COUN

T

EDCD

EDCA

7

EDCA

6

EDCA

5

EDCA

4

EDCA

3

EDCA

2

EDCA

1

EDCA

0

TYPE

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

RESET

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0