Tstgta, Test for greater than zero (agu), Instruction formats and opcodes instruction fields – Freescale Semiconductor StarCore SC140 User Manual

Page 735: Operation assembler syntax, Tstgta r2

TSTGTA

SC140 DSP Core Reference Manual

A-421

TSTGTA

Test for Greater Than Zero (AGU)

TSTGTA

Description

Status and Conditions that Affect Instruction

Status and Conditions Changed by Instruction

Example

tstgta r2

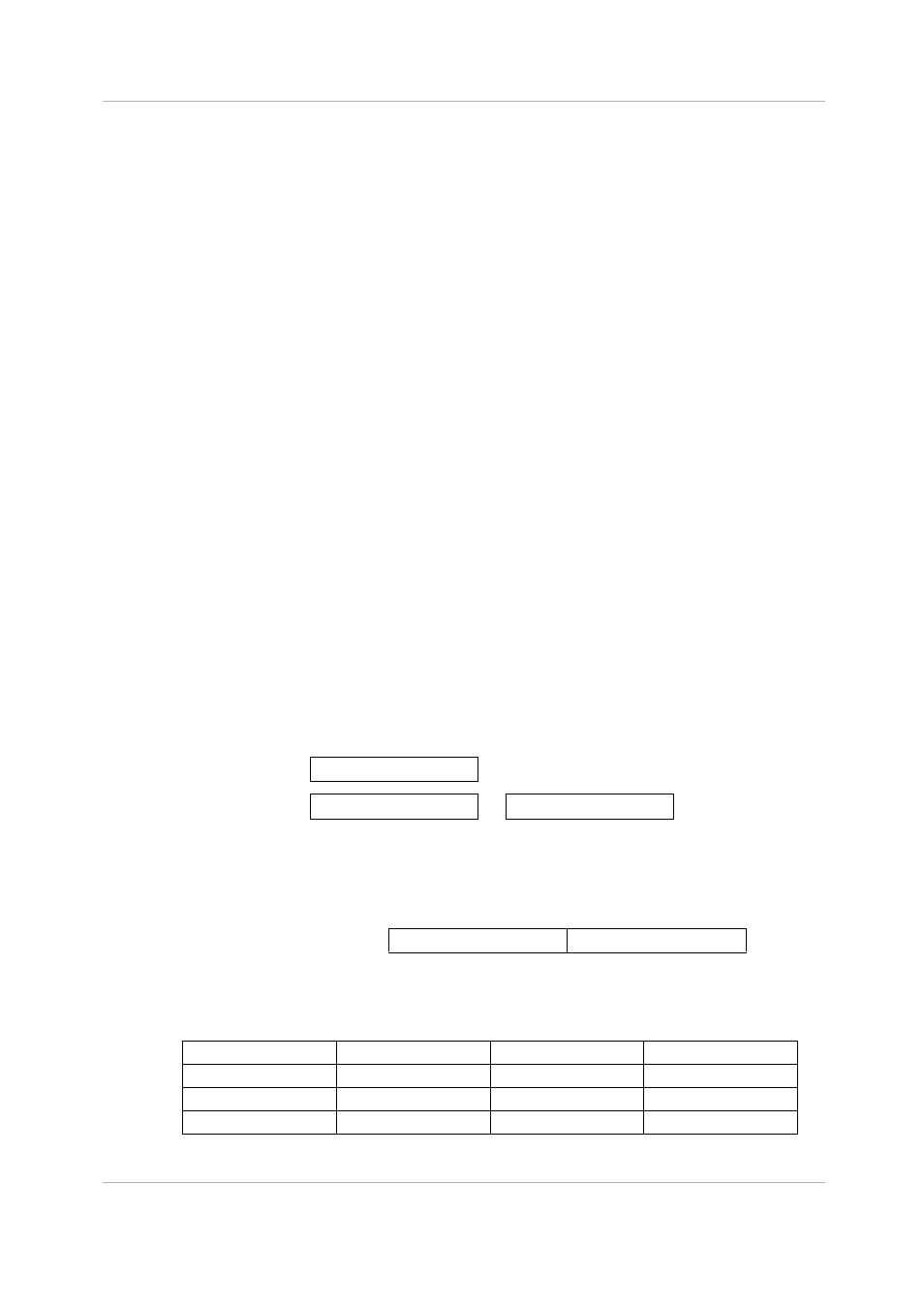

Instruction Formats and Opcodes

Instruction Fields

Rx

RRRR

AGU Source/Destination Register

Operation

Assembler Syntax

If Rx

> 0, then 1 → T, else 0 → Τ

TSTGTA Rx

TSTGTA Rx

Sets the T bit if the source AGU register (Rx) is greater than zero; otherwise, clears the T bit.

Register Address

Bit Name

Description

SR[18]

EXP

Determines which stack pointer is used when the stack pointer is an

operand. Otherwise, the instruction is not affected by SR.

Register Address

Bit Name

Description

SR[1]

T

Set if the source operand is greater than zero and cleared if the source

operand is not greater than zero.

Register/Memory Address

Before

After

R2

$46EA 2BE8

SR

$00E4 0000

$00E4 0002

Instruction

Words Cycles Type

Opcode

15

8

7

0

TSTGTA Rx

1

1

2

1

1

1

0

R R R R

1

1

1

1

0

0

1

0

0000

N0

0100

—

1000

R0

1100

R4

0001

N1

0101

—

1001

R1

1101

R5

0010

N2

0110

—

1010

R2

1110

R6

0011

N3

0111

SP

1011

R3

1111

R7

Note:

This instruction can specify R8-R15 as operands by using a high register prefix.