Freescale Semiconductor StarCore SC140 User Manual

Page 748

SC140 DSP Core Reference Manual

In SC100 implementations, the SCID is defined at the SoC level by strapping a set of core interface signals

that define the REVNO and CORETP fields during reset. Therefore, all SoC designs must conform to the

SCID to derive the core identification benefits for host-based software tools and run-time software.

The SCID should not be used for SoC or mask set identification outside the control of StarCore.

SC100-based products should add an off-core SoC or mask set identification register, independent of the

SCR. The SCR is used only for on-core identification.

The SCID may assist in migrating applications software and software development tools across StarCores.

Software tools developers and run-time software need to assess the whole SCID (both REVNO,

RESERVED and CORETP fields) to determine possible code migration from core to core. Note that the

SCR does not guarantee identical timing across SCIDs.

For the same CORETP, software written for a lower REVNO will produce the same results on a higher

REVNO except where the higher REVNO introduces a bug fix to an existing instruction. These bug fixes

may present software migration and tools issues.

For the same REVNO, software written for a lower CORETP may not run on a higher CORETP because

CORETP is not a monotonic scalability index. A higher CORETP may have more or less execution units

and VLES grouping capabilities than a lower CORETP. For example, software written for the SC140

(CORETP = 001) will not run and produce the same results on a dual-MAC SC100, having the same or

higher REVNO. Software tools developers and run-time software need to be aware of the actual CORETP

software migration issues.

For historical reasons, the CORETP field of the Rainbow product is 000 instead of 001. However the SW

tools should consider this product as identical with the MCS8101 rev0 product.

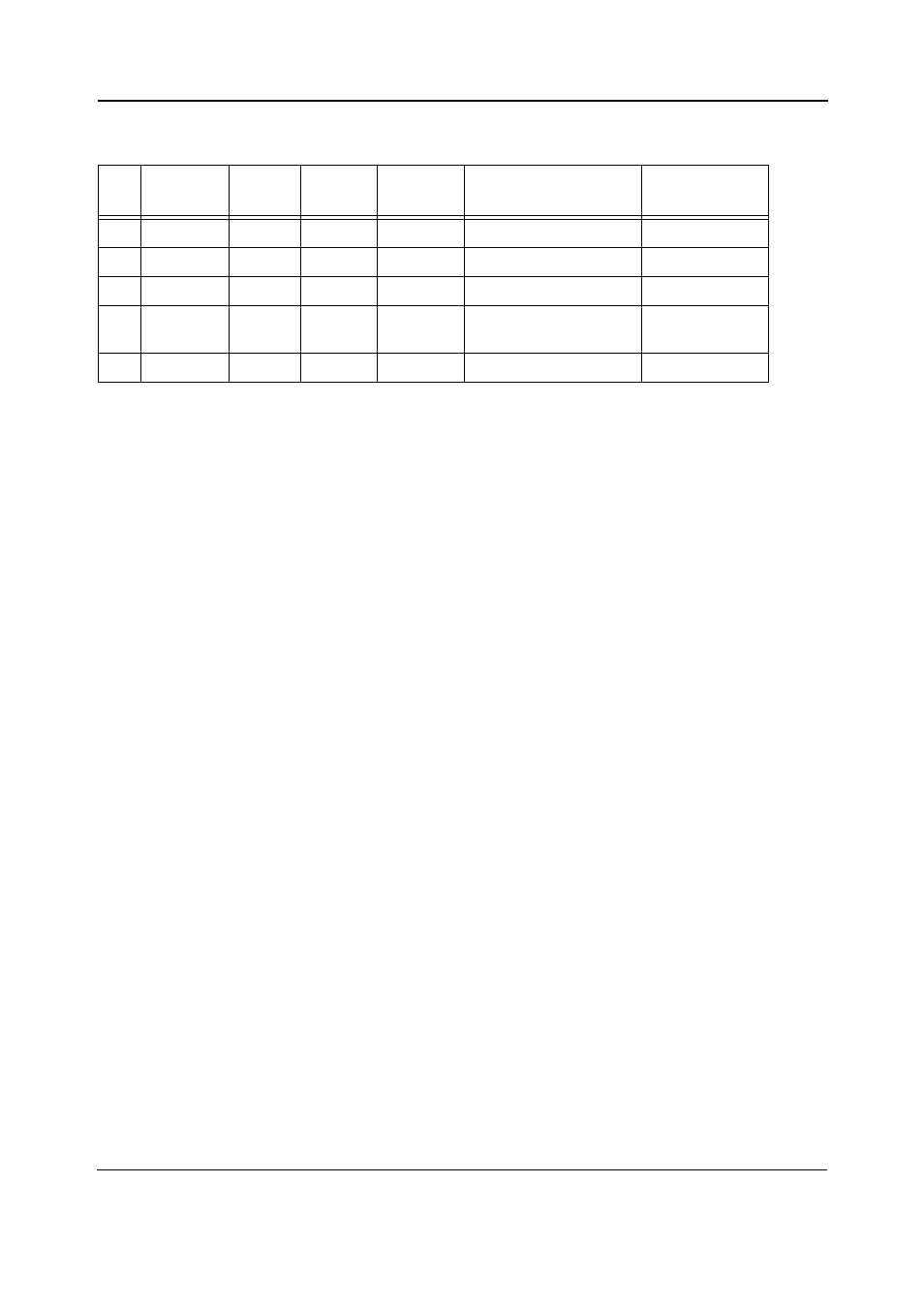

Table B-1. SCID Assignments

Hex

SCID

Bits 23-21

REVNO

Bit 20

Reserved

Bits 19-17

CORETP

Instruction

Set Version

Cores

Example

SoC / platform

00

000

0

000

Original

SC140 rev 0

Pre-Chip

10

001

0

000

V1

SC140 rev 0_1

MSC8101 rev0

11

001

0

001

V1

SC140 rev 0_1

Rainbow

21

010

0

001

V2

SC140 rev A

MSC8102

MCS8101 revA

31

011

0

001

V3

SC140e

P2002