6 eonce register addressing, Trace buffer register set -30, Own in table 4-11 – Freescale Semiconductor StarCore SC140 User Manual

Page 140

4-30

SC140 DSP Core Reference Manual

EOnCE Register Addressing

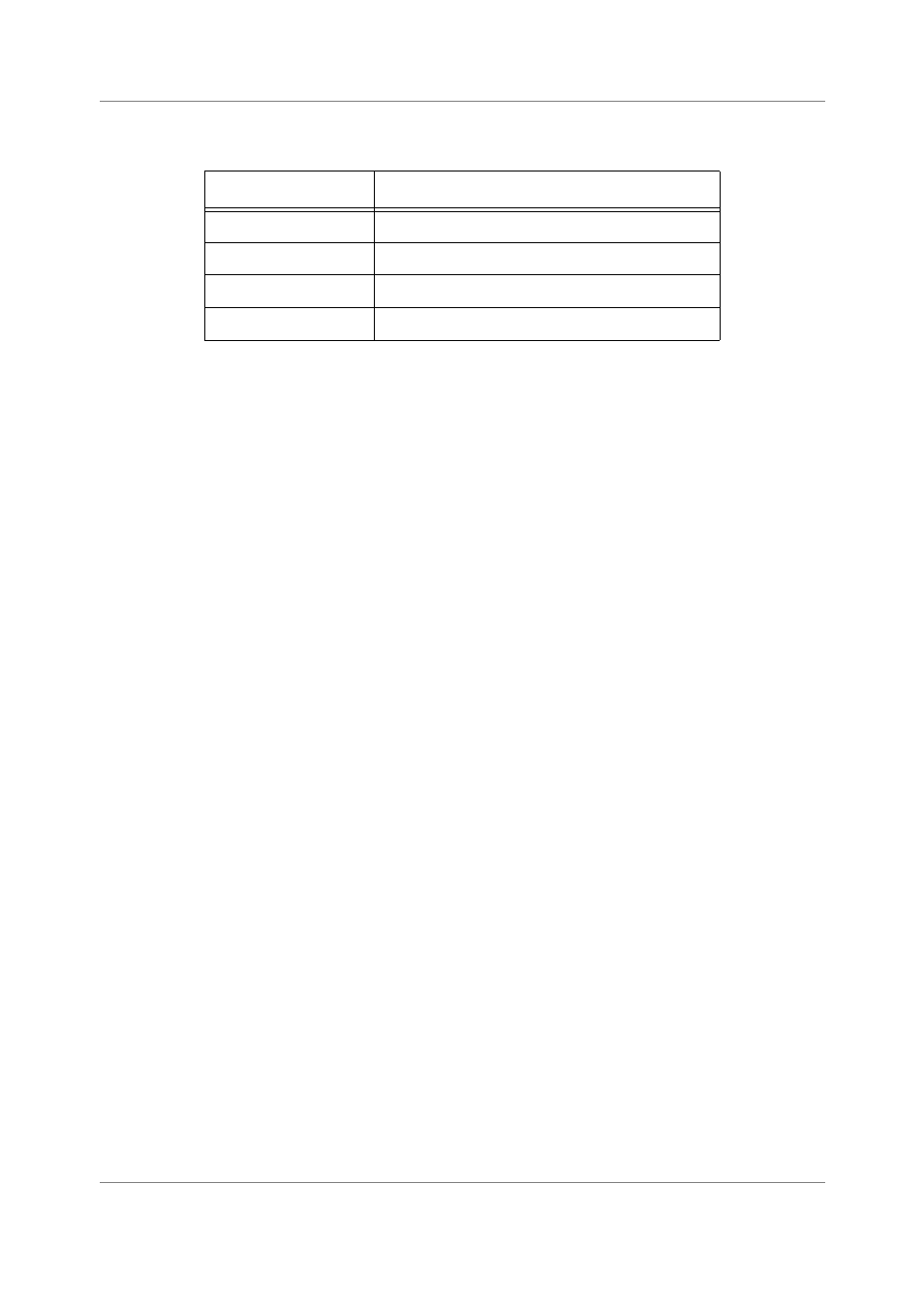

Table 4-11. Trace Buffer Register Set

The functionality of the trace unit registers is described in

Section 4.11, “Trace Unit Registers.”

4.6 EOnCE Register Addressing

The various units described above use a large number of registers. The EOnCE registers can be read or

written when the core is running, or when the core is in debug state.

All the EOnCE registers accessible from the core (either for read or write operations) are memory mapped.

This means that each register has its own address in the memory space. The memory address of an EOnCE

register is defined by adding four times the register address offset from Table 4-12 on page 4-31 to the

EOnCE register base address defined for each SoC derivative. For example, the memory address for the

LSB part of register ERCV is $8 + rba_via, where rba_via is the derivative dependent register base

address.

Most EOnCE memory-mapped registers allow only 32-bit accesses except the status, monitor, and control

registers (ESR, EMCR, EE_CTRL, EDCA[0-5]_CTRL, EDCD_CTRL, ECNT_CTRL, ESEL_CTRL, and

TB_CTRL). The latter support 16-bit accesses, which enable the use of bit-mask operations. There is only

one access per execution set for all EOnCE registers. When a 16-bit access is used on the 32-bit long ESR

and EMCR registers, the software address offset to the MSB part of the registers is equal to the software

address offset of the LSB part + 2.

Registers longer than 32 bits are accessed as two registers.

As described in

Section 4.2.6, “Reading/Writing EOnCE Registers Through JTAG,”

each EOnCE unit has

a shift register supporting the EOnCE registers of this unit. In some cases, the “shift width” of the EOnCE

register is longer than its actual width.

Register Name

Description

TB_CTRL

Trace buffer control register

TB_RD

Trace buffer read pointer register

TB_WR

Trace buffer write pointer register

TB_BUFF

Trace buffer virtual register