2 one-word low register prefix, 3 conditional execution, One-word low register prefix -9 – Freescale Semiconductor StarCore SC140 User Manual

Page 189: Conditional execution -9, Prefix instructions -9, Conditional ifc syntax -9, Section 5.2.3, “conditional, Execution

Instruction Grouping

SC140 DSP Core Reference Manual

5-9

5.2.2.2 One-Word Low Register Prefix

The One-Word Low register prefix encodes all information of the two-word prefix, except for encoding for

high registers. It is used whenever no instruction in the VLES uses a high register, and a prefix is needed

for one of the other reasons: instruction grouping that cannot be done with serial grouping, conditional

execution of the whole VLES or a sub-group, and encoding for HW loop support.

5.2.3 Conditional Execution

Certain instructions are executed conditional on the state of the T-bit in the status register (SR). For

example, JT (Jump if True) is executed only if the T-bit is set. The SC140 also supports conditional

execution of a group or subgroup of instructions in an execution set. A group or subgroup represents the

instructions that may be conditionally executed depending upon a single condition encoded in the prefix.

The single condition is specified by the following prefix instructions:

For example:

IFT

ADD D0,D1,D2

MOVE.L (R0)+,D0

The set as a whole (including the ADD and MOVE instructions) is executed only if the T-bit is set. The

instructions in the subgroups may themselves be conditional. For example, using MOVEc, TFRc and Jc

can add further conditional control. However, the subgroups themselves may not contain another IFc

instruction.

If no IFc instructions exist in the execution set, the default is the unconditional execution of the whole set.

For finer control, it is possible to split the instructions in the execution set into two subgroups 1 and 2,

conditionally controlling the execution of each subgroup independently. Refer to

“Instruction Reordering Within an Execution Set,”

for information about how the assembler reorders

instructions for encoding conditional execution sets.

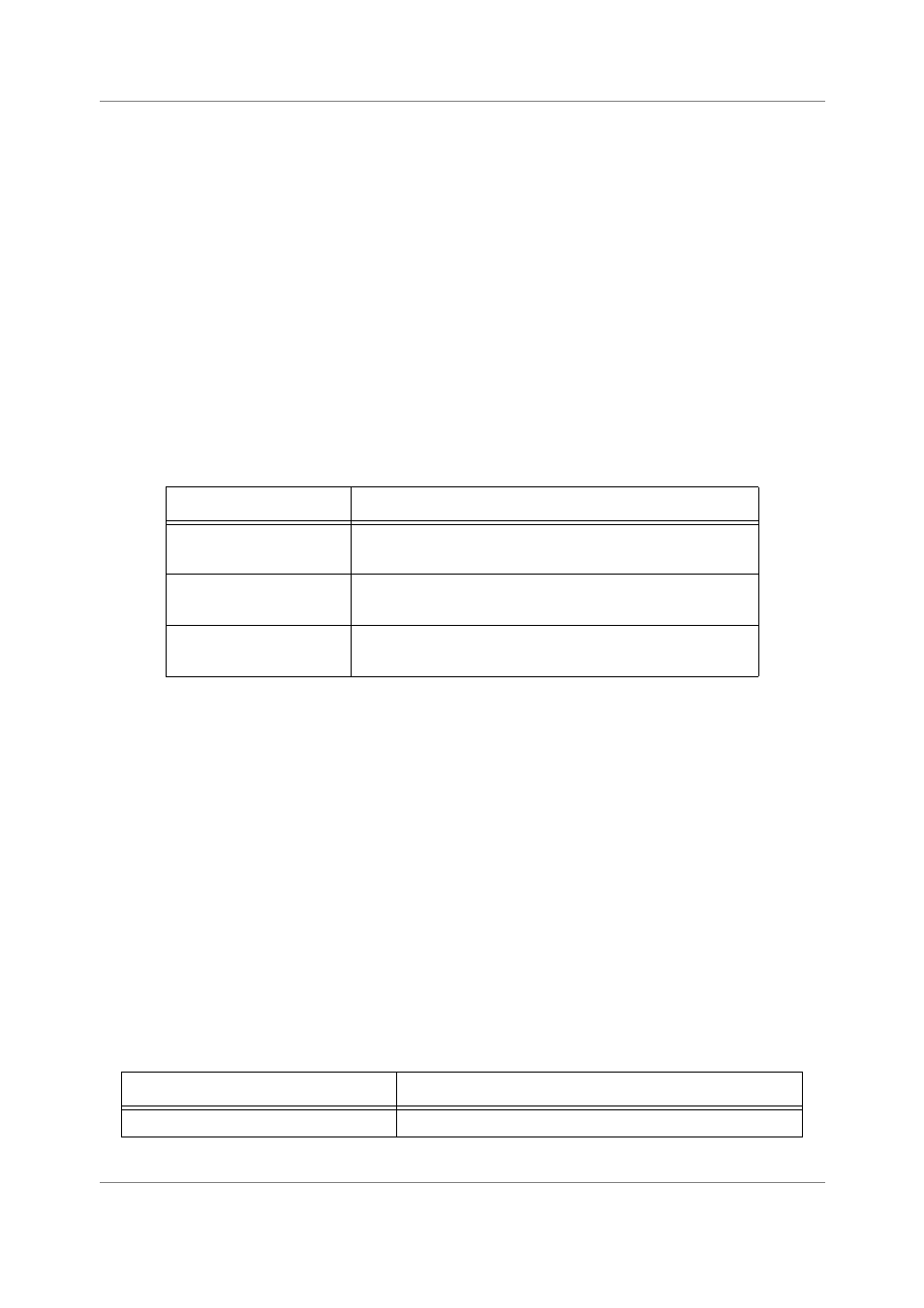

Table 5-4 displays the conditional IFc syntax. In the table, [inst] represents optional additional instructions.

Refer to

Section 7.5.3, “Prefix Grouping Rules,”

on page 7-11 for the IFc programming rules.

Table 5-3. Prefix Instructions

Instruction

Description

IFT (if true)

Execute the group or subgroup if the T bit is set

IFF (if false)

Execute the group or subgroup if the T bit is clear

IFA (if always)

Execute the group or subgroup unconditionally

Table 5-4. Conditional IFc Syntax

Assembly Syntax

Meaning

[IFA] inst [inst]

Unconditional execution of the VLES