5 memory access width, 6 memory access misalignment, Memory access width -42 – Freescale Semiconductor StarCore SC140 User Manual

Page 74: Memory access misalignment -42

2-42

SC140 DSP Core Reference Manual

Address Generation Unit

2.3.3.5 Memory Access Width

The SC140 core supports variable width access to data memory. With every memory access, the core sends

one of four signals to the memory interface to designate whether the access width is 8 bits, 16 bits, 32 bits,

or 64 bits wide. The access width is determined by the type of MOVE instruction being used. For example,

MOVE.B is used for byte access. MOVE.W is used for word access. For long-word access, MOVE.L,

MOVE.2F, and MOVE.2W are used. And, for two long-word access, MOVE.2L, MOVE.4F, and

MOVE.4W are used.

The memory addresses are always in units of bytes. For example, addresses for two-word MOVE

operations to/from memory are available in multiples of four in order to best align the data with the byte

addressing.

Address calculations and register update calculations are performed according to the memory access width

as shown in Table 2-18.

2.3.3.6 Memory Access Misalignment

Each access to the memory generated by the core should be aligned according to the access type. If the

alignment rule is violated, erroneous data may be fetched from the memory. In addition, an exception may

be generated to identify that an unaligned access occurred. For more information, see

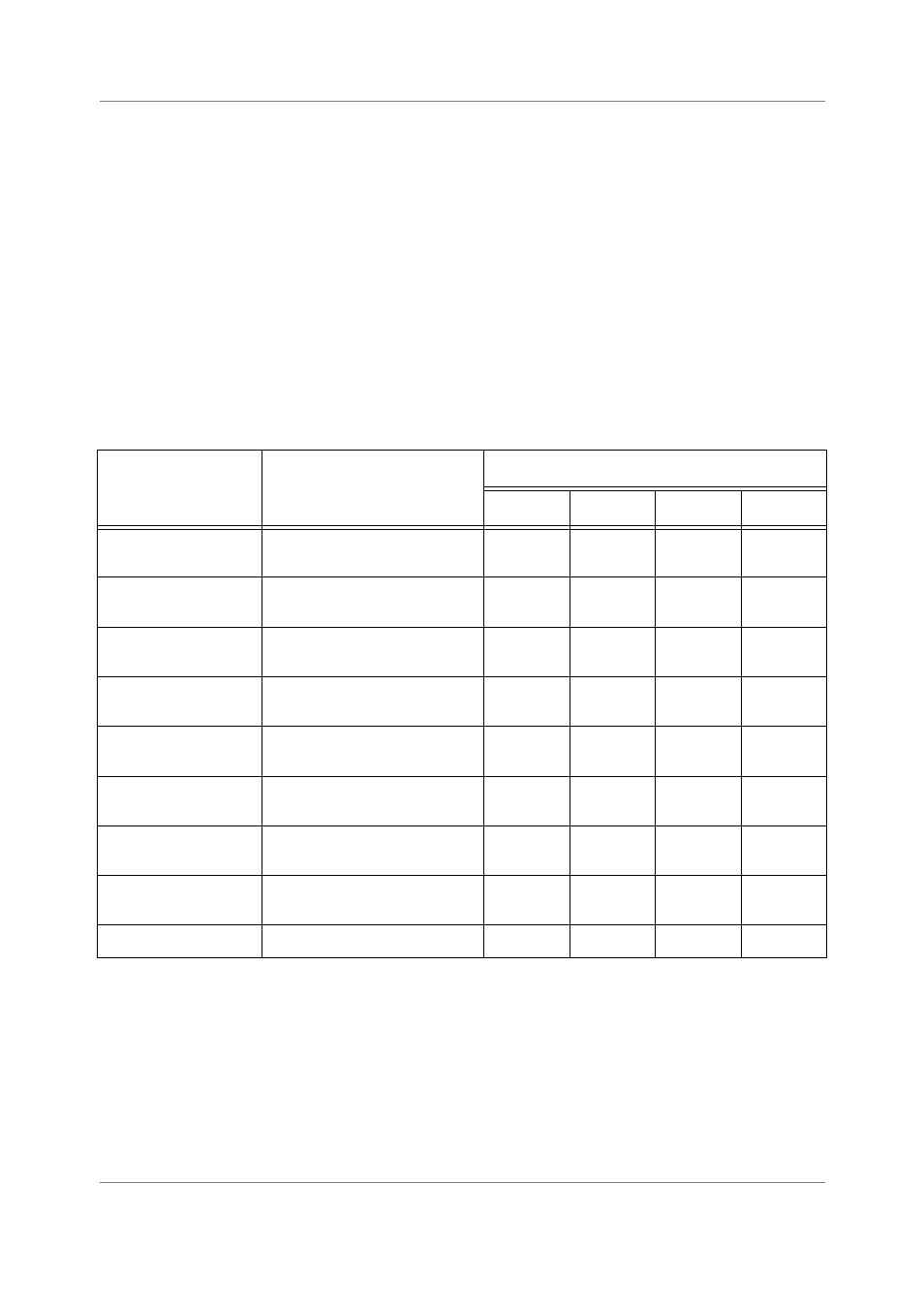

Table 2-18. Access Width Support for Address and Register Update Calculations

Addressing Mode

Calculation

Memory Access Width

Byte

Word

Long

Two Long

Post-increment (Rn) +

Post-decrement (Rn) -

Rn register post-increment or

post-decrement by —>

1

2

4

8

Post-increment by

Offset (Rn)+Ni

Rn register post-increment by ->

Ni*1

Ni*2

Ni*4

Ni*8

Indexed by Offset N0

(Rn + N0)

Actual address offset

N0

2*N0

4*N0

8*N0

Indexed by Address

Register Rm (Rn + Rm)

Actual address offset

Rm

2*Rm

4*Rm

8*Rm

Short Displacement

(Rn + x)

Actual address displacement

x

x

x

x

Word Displacement

(Rn + xxxx)

Actual address displacement

xxxx

xxxx

xxxx

xxxx

SP update in Push/Pop

SP post-increment or

pre-decrement by —>

8

8

8

8

SP Short Displacement

(SP - xx)

Actual address displacement

NA

xx

xx

NA

SP Word Displacement

Actual address displacement

xxxx

xxxx

xxxx

xxxx