Freescale Semiconductor StarCore SC140 User Manual

Page 104

3-4

SC140 DSP Core Reference Manual

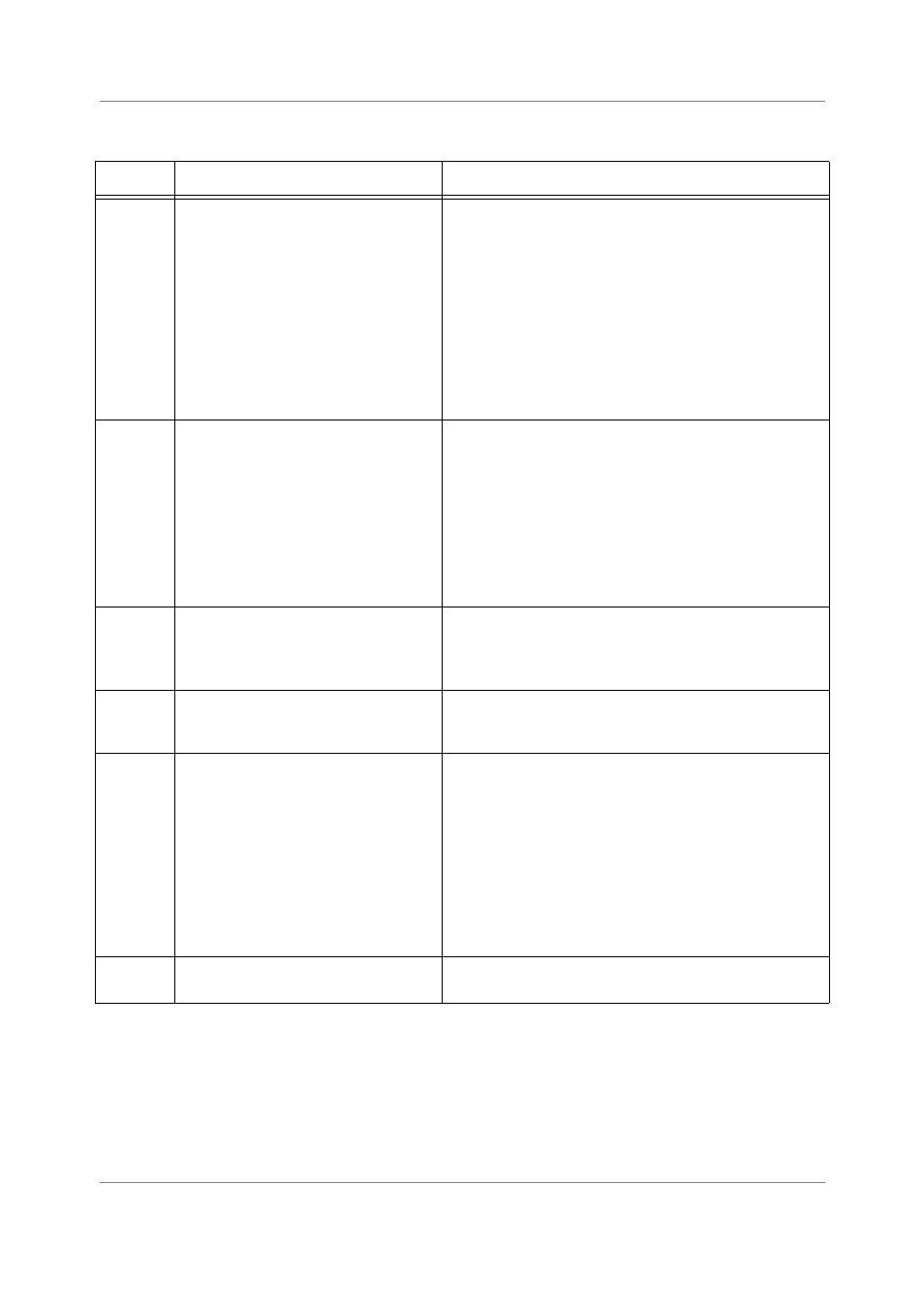

Core Control Registers

OVE

Bit 20

Overflow Exception Enable Bit —

Enables or disables the generation of an

exception caused by an overflow. The

DOVF bit in EMR is always set when an

overflow occurs. If the OVE bit is set and

the DOVF bit is already set, no exception

is generated until the DOVF bit is cleared

and set again.

See

Section 3.1.2, “Exception and Mode

for more information.

This bit is cleared at core reset.

0 = Overflow exception generation is disabled

1 = Overflow exception generation is enabled, unless DOVF

bit in EMR is already 1

DI

Bit 19

Disable Interrupts Bit — When this bit

is set, no maskable interrupts are

serviced, regardless of the IPL values,

which remain unchanged.

This bit can be set with the DI instruction,

which ensures that interrupts are

masked immediately, and can be cleared

with the EI instruction.

This bit is cleared at core reset.

0 = Interrupts enabled

1 = Interrupts disabled

EXP

Bit 18

Exception Mode Bit — Selects the

active stack pointer and working mode of

the core.

This bit is set at core reset.

0 = Normal working mode, active SP is NSP

1 = Exception working mode, active SP is ESP

R

Bits

17–12

Reserved

VF3–VF0

Bits 11–8

Viterbi Flags — Reflect the status of the

two parallel conditional transfers in the

MAX2VIT instruction. These flags are

generally used in conjunction with the

VSL instructions. Two Viterbi flags can

be independently set or cleared

according to the MAX2VIT result.

For more information, see MAX2VIT and

VSL in

These bits are cleared at core reset.

0 = Appropriate 16-bit portion transferred

1 = Appropriate 16-bit portion not transferred

R

Bit 7

Reserved

Table 3-1. Status Register Description (Continued)

Name

Description

Settings