Freescale Semiconductor StarCore SC140 User Manual

Page 149

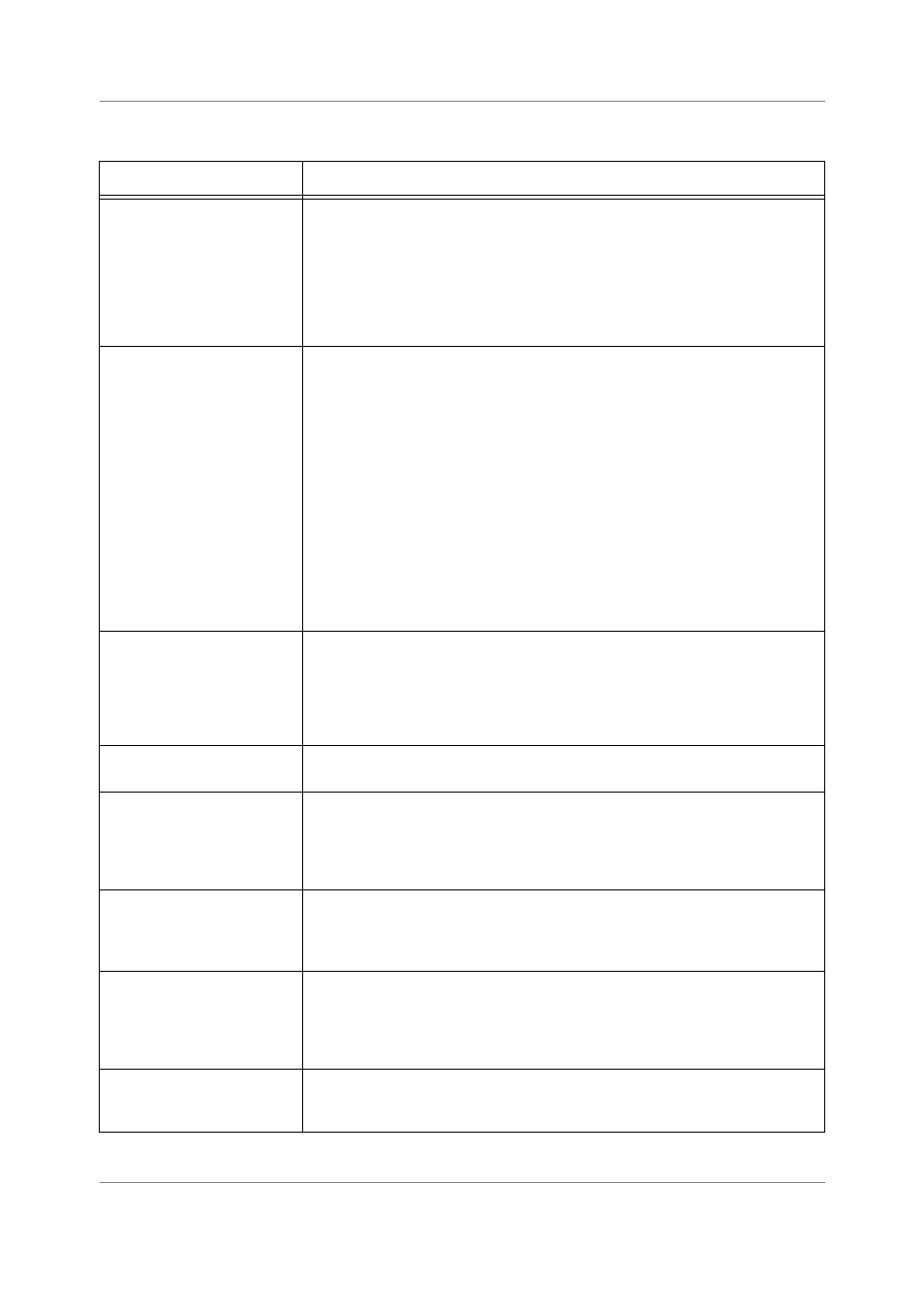

EOnCE Controller Registers

SC140 DSP Core Reference Manual

4-39

TBFULL

Bit 25

Trace Buffer Full — Indicates that the trace buffer of EOnCE is full. In order not to

lose addresses when TBFDM and IME bits in the EMCR register are set (when TB

is full), the bit causes a debug exception. The TBFULL bit is set when the TB write

pointer equals TB-size minus 15, where TB-size is defined for each SoC

derivative. TB-size is the size of the off-core trace buffer memory and is defined by

the value of 16 core external signals. The TBFULL bit is reset when the trace

buffer is enabled. For more information, see

Section 4.5.5.3, “Reading the Trace

NOCHOF

Bit 24

No Change-of-Flow (COF) in Debug State — If this read-only status bit is set by

EOnCE upon entering debug state, users cannot inject a change-of-flow

instruction through the EOnCE to the core. This occurs when the core is in the

following locations:

•

Immediately after executing a delayed change of flow instruction (see

)

•

At the end of a long loop, right after executing LA-2 or LA-1 (see

)

•

During a short loop

.

Single-step operations can be used in order to exit this state. When debug state is

entered in the middle of a short loop, the loop counter (LC) should be reset and

some single-step operations should be executed before injecting a JMP

instruction.

If this bit is set right before intended return to execution (with the EX bit in ECR),

one single-step should be performed before exiting debug state.

REVNO

Bits 23–21

Revision Number — The REVNO field generally identifies the basic instruction

set revision of the core. It identifies the availability of new instructions and

corrections to existing instructions along a binary upward compatible roadmap.

Changes in REVNO imply a software tools switch, different software simulator and

different host debugger. Cores of different revisions can differ in their EOnCE

programming model.

R

Bit 20

Reserved

CORETP

Bits 19–17

Core Type — The CORETP field identifies the architecture member within the

SC100 family. It identifies the availability of new execution units and VLES

grouping capabilities. Note that execution units and VLES can scale up or down

without altering the basic instruction set. Changes in CORETP imply a software

tools switch, different software simulator, and different host debugger.

DRTBFULL

Bit 16

Debug Reason is Trace Buffer — Set when the core enters debug state or

executes a debug exception as a result of the EOnCE trace buffer being full

(TBFULL set). It is cleared by EOnCE when the core exits debug state, or when

the DIS bit in EMCR is reset by the user.

DRSW

Bit 15

Debug Reason is Software Debug — Set when the core enters debug state or

executes a debug exception as a result of the execution of a debug instruction in

the core. DRSW is also set when an execution of the DEBUGEV instruction puts

the DSP into debug state. It is cleared by EOnCE when the core exits debug state,

or when the DIS bit in EMCR is reset by the user.

DREE4

Bit 14

Debug Reason is EE4 — Set when the core enters debug state or executes a

debug exception as a result of EE4 assertion. It is cleared by the EOnCE when the

core exits debug state, or when the DIS bit in EMCR is reset by the user.

Table 4-14. ESR Description (Continued)

Name

Description