3 execution state, 4 reset processing state, Execution state -43 – Freescale Semiconductor StarCore SC140 User Manual

Page 223: Reset processing state -43, T occurs, as described in, Section 5.7.4, “reset processing state

Processing States

SC140 DSP Core Reference Manual

5-43

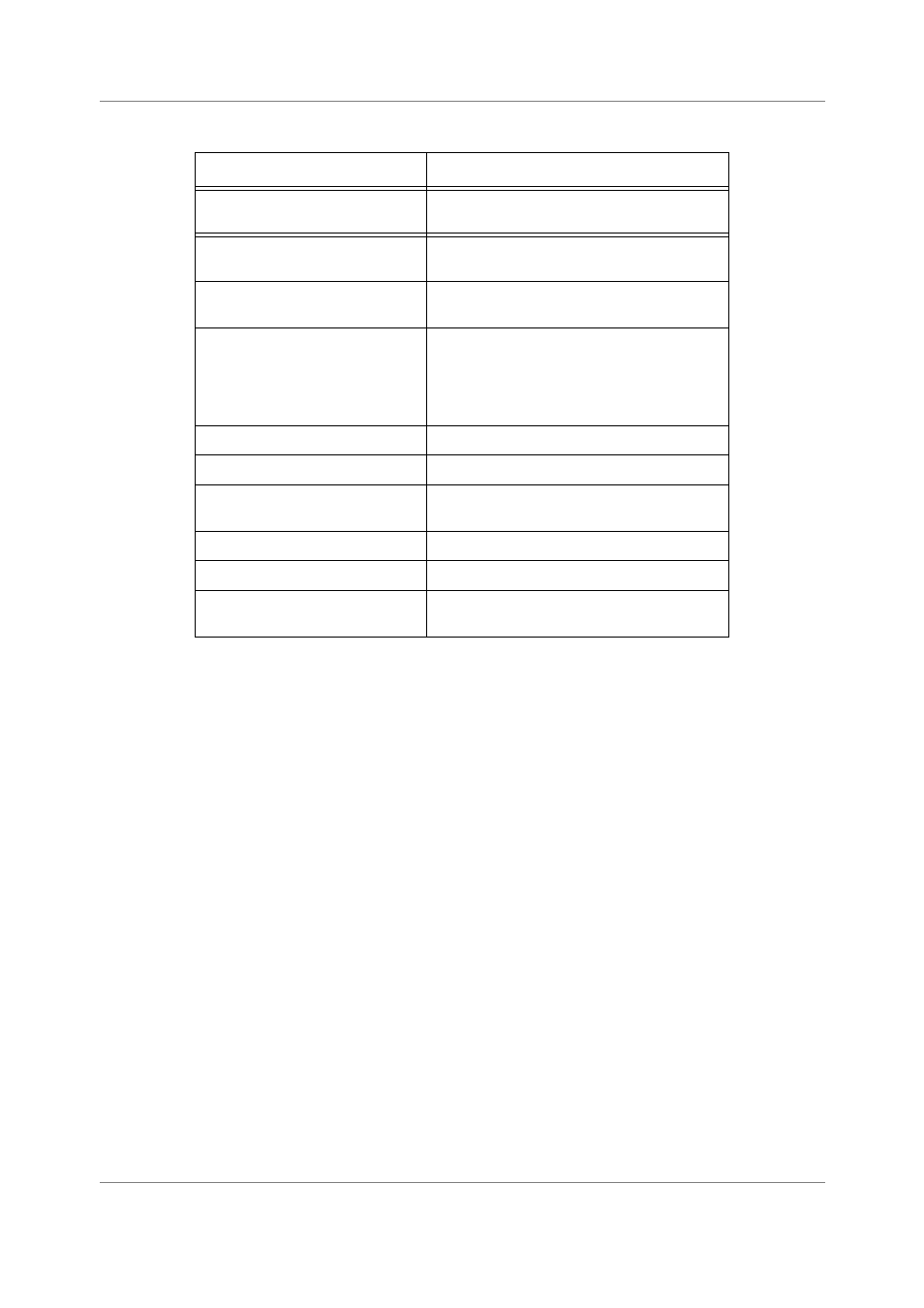

Table 5-17. Processing State Transitions

5.7.3 Execution State

The execution state is where instructions are repeatedly fetched and executed. All software runs in the

execution state.

5.7.4 Reset Processing State

The reset processing state is entered when an external core hardware reset occurs. Upon entering the reset

state, the following registers are updated with their reset values:

•

SR

•

EMR

•

VBA

•

MCTL

Chapter 3, “Control Registers,”

for details on the reset of the various bits of the above registers.

The core remains in the reset state until the end of hardware reset. Upon leaving the reset state, the core

enters the exception working mode, as part of the execution state, and program execution begins at a

derivative-dependent program memory address.

Processing State Transitions

Description

1, 2, 3, 4

Assertion of one of the core hardware reset

input signals.

5

De-assertion of reset if EE0 or a JTAG debug

command is asserted during reset

6, 7

Entering debug state through an external

request (JTAG, EE pin or system input).

8

Entering debug state through execution of

debug/debugev, or occurrence of EOnCE

events as programmed in the activated

EOnCE, or an external request ((JTAG, EE pin

or system input)

9

Executing the STOP instruction.

10

Executing the WAIT instruction.

11

De-assertion of the reset signal, assuming

EE0 not asserted.

12

Assertion of one of the exit from STOP signals.

13

Assertion of an unmasked interrupt request.

14

Programming change to the EOnCE control

registers through the JTAG.