2 real-time jtag access, Real-time jtag access -33, Section 4.6.1, “reading or – Freescale Semiconductor StarCore SC140 User Manual

Page 143: Writing eonce registers using core software, For further details

EOnCE Register Addressing

SC140 DSP Core Reference Manual

4-33

4.6.1 Reading or Writing EOnCE Registers Using Core

Software

The core can read or write most EOnCE registers from the software. Software access can be disabled by

the SWDIS bit in the EMCR register. For more information, see

Section 4.7.3, “EOnCE Monitor and

In cases where the core is being accessed by the software and the JTAG port at the same time, the JTAG

access has priority over the software access.

4.6.2 Real-Time JTAG Access

The EOnCE registers could be read or written to by the host through the JTAG port, as described in

Section 4.2.6, “Reading/Writing EOnCE Registers Through JTAG.”

When the core is not in debug state and the host is accessing the EOnCE registers from the JTAG port,

there is a possibility that an EOnCE command may be lost due to a long core stall. To ensure correct

execution of a command, the user should read a special ACK bit by shifting out the JTAG IR register

together with the core status bits. If the bit is set, this indicates that the last EOnCE command was

successfully executed. This bit is reset each time a new command is shifted from the JTAG port to the

EOnCE.

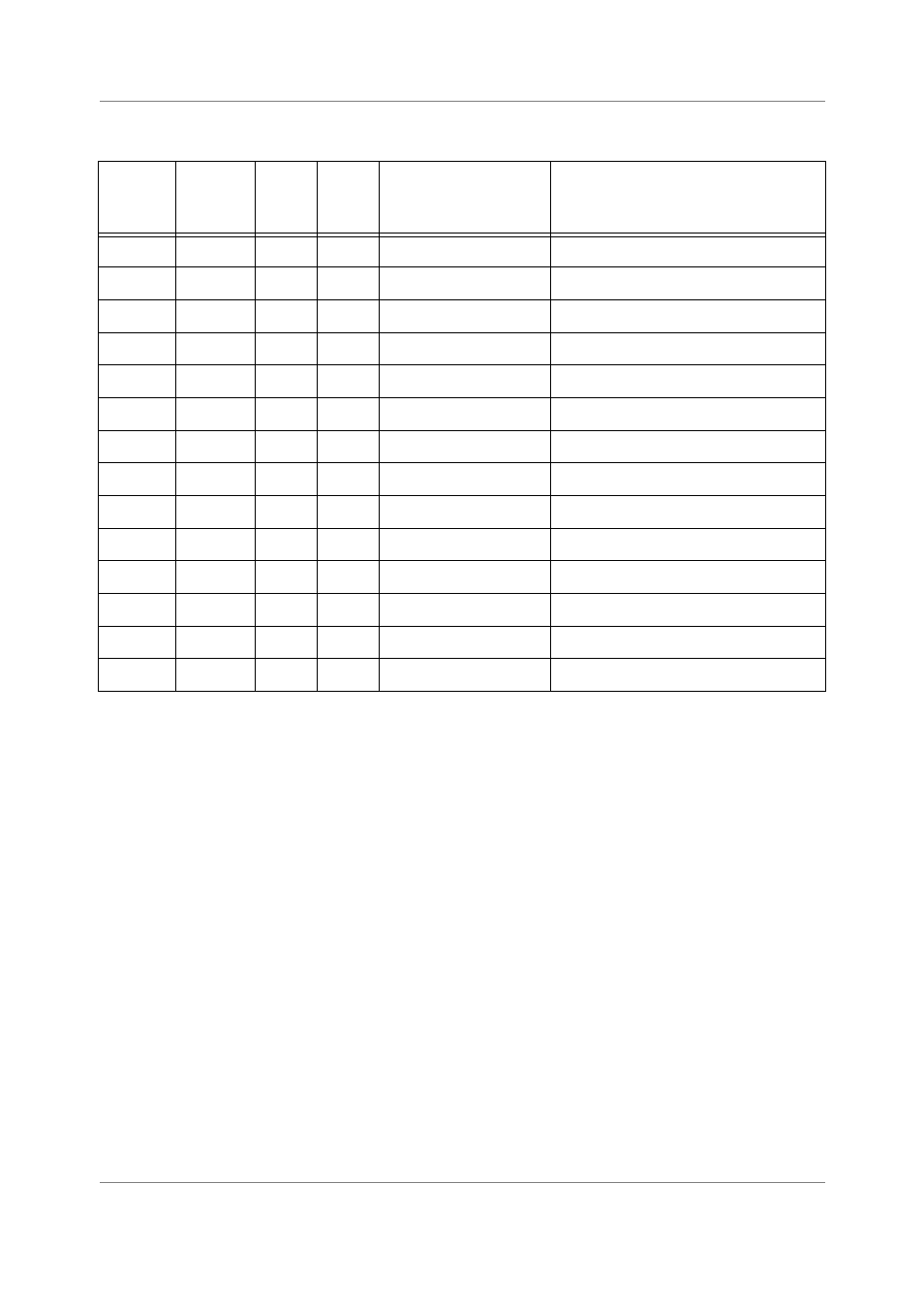

49

R/W

16

16

ESEL_DM

Selector DM mask

4A

R/W

16

16

ESEL_DI

Selector DI mask

4B

Reserved address

4C

R/W

16

16

ESEL_ETB

Selector enable TB mask

4D

R/W

16

16

ESEL_DTB

Selector disable TB mask

4E

Reserved address

4F

Reserved address

50

R/W

16

32

TB_CTRL

Trace buffer control register

51

R/W

16

32

TB_RD

Trace buffer read pointer

52

R/W

16

32

TB_WR

Trace buffer write pointer

53

R

32

32

TB_BUFF

Trace buffer

..........

..........

Reserved addresses

7E

NO

48

48

CORE_CMD

Core command register

7F

NO

NOREG

No register selected

Table 4-12. EOnCE Register Addressing Offsets (Continued)

EOnCE

Register

Offset

Software

Access

Width

Shift

width

Register Name

Description