Unsupported features, Interface, Unsupported features -2 – Altera Embedded Peripherals IP User Manual

Page 88: Interface -2

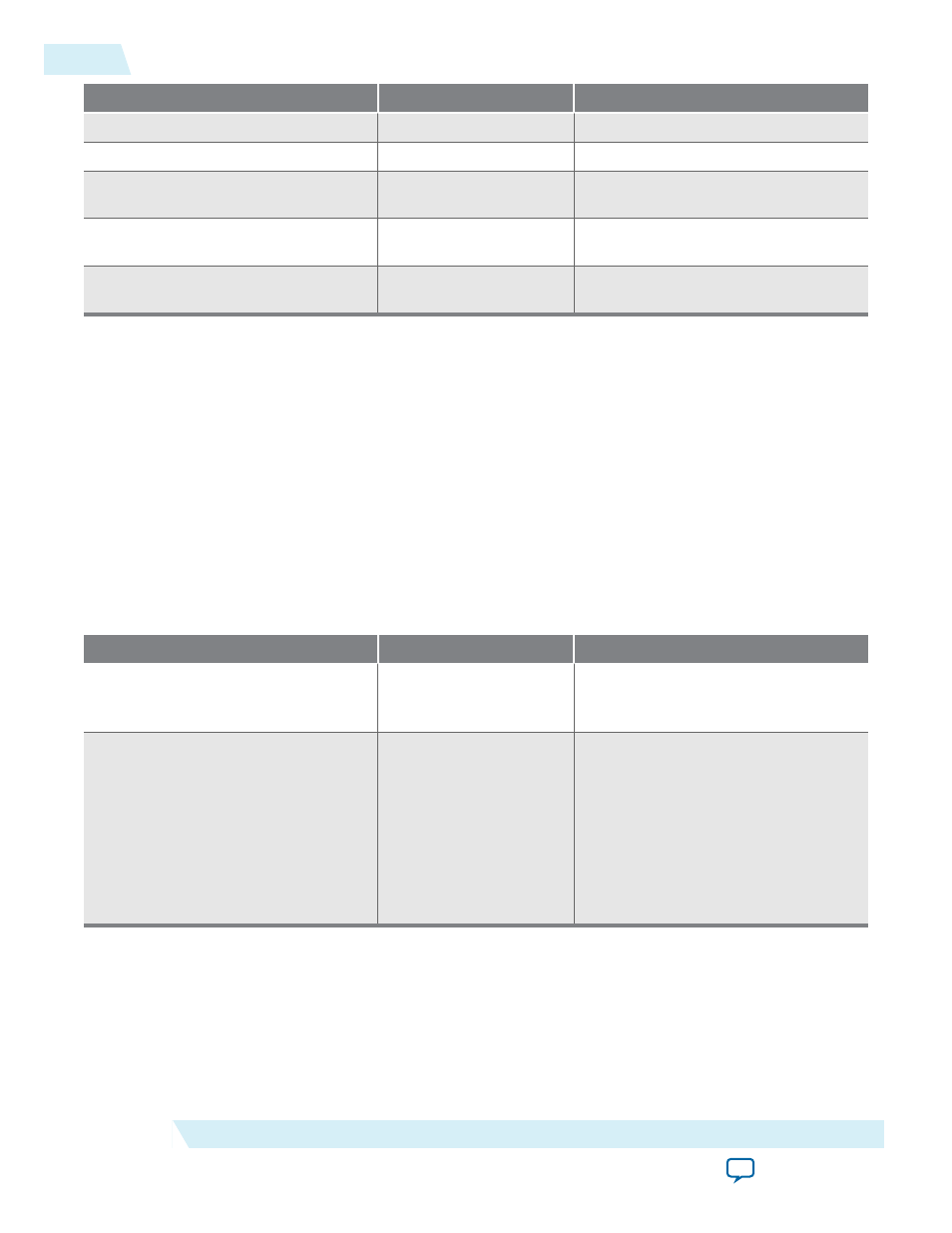

Features

Run Time Configurable

Generate Time Configurable

Even/Odd parity

Yes

-

Baud rate selection

Yes

-

Priority based interrupt with configu‐

rable enable

Yes

-

Hardware Auto Flow Control (cts_n/

rts_n signals)

Yes

Yes

DMA Extra (configurable support for

extra DMA sideband signal)

Yes

Yes

Note: When a feature is both Generate time and Run time configurable, the feature must be enabled

during Generate time before Run time configuration can be used. Therefore, turning ON a feature

during Generate time is a prerequisite to enabling/disabling it during run time.

Unsupported Features

Unsupported Features vs PC16550D:

• Separate receive clock

• Baud clock reference output

Interface

The Soft UART will have the following signal interface, exposed using

_hw.tcl

through Qsys software.

Table 9-2: Clock and Reset Signal Interface

Pin Name

Direction

Description

clk

Input

Avalon clock sink

Clockrate: 24 MHz (minimum)

rst_n

Input

Avalon reset sink

Asynchronous assert, Synchronous

deassert active low reset.

Interconnect fabric expected to

perform synchronization – UART

and interconnect is expected to be

placed in the same reset domain to

simplify system design

9-2

Unsupported Features

UG-01085

2014.24.07

Altera Corporation

16550 UART