Altera Embedded Peripherals IP User Manual

Page 180

Control Register Interface

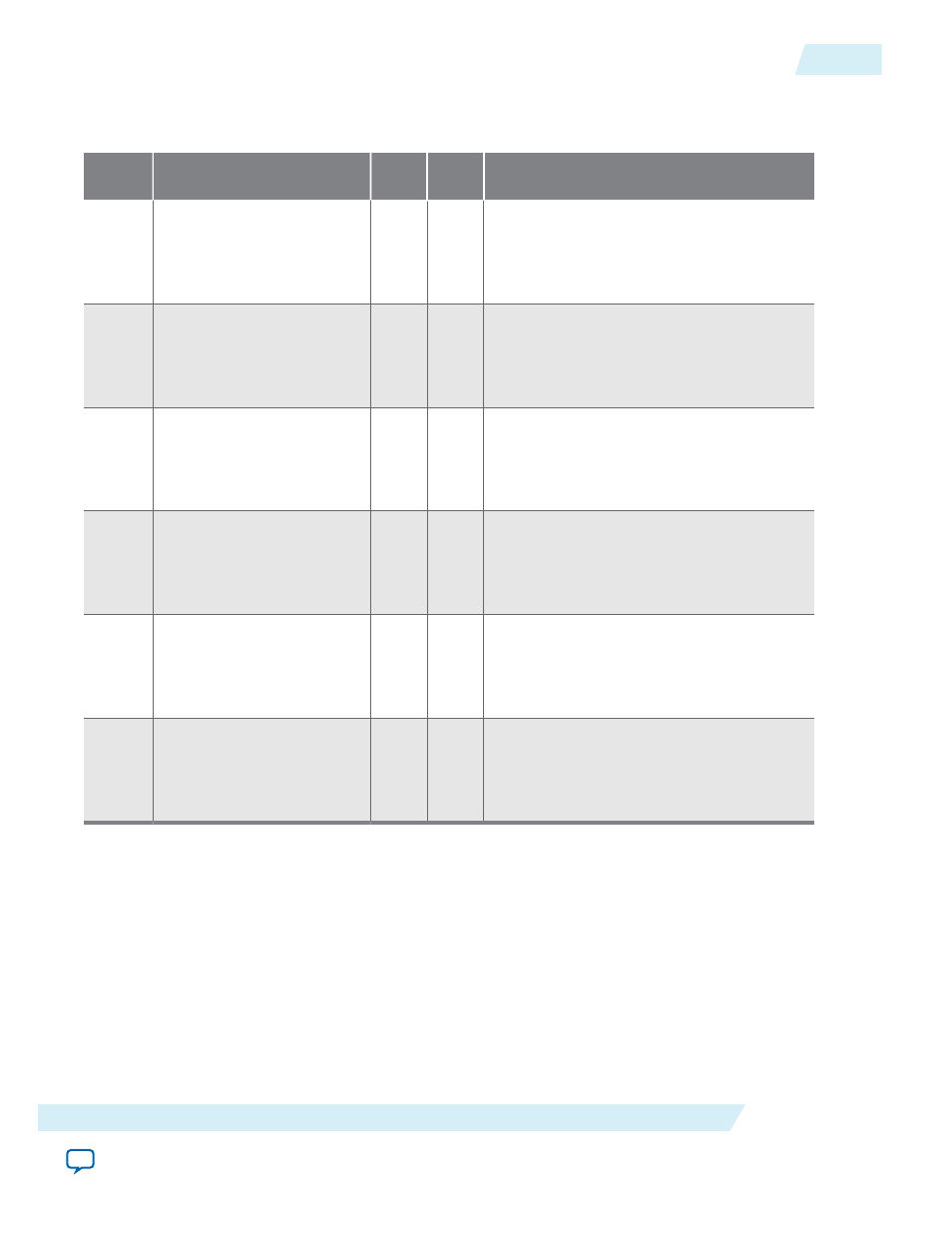

Table 17-6: Control Interface Register Map

Byte

Offset

Name

Access Reset

Value

Description

0

ALMOST_FULL_THRESHOLD

RW

0

Primary almost-full threshold. The bit

Almost_full_data[0]

on the Avalon-ST

almost-full status interface is set to 1 when

the FIFO level is equal to or greater than

this threshold.

4

ALMOST_EMPTY_

THRESHOLD

RW

0

Primary almost-empty threshold. The bit

Almost_empty_data[0]

on the Avalon-ST

almost-empty status interface is set to 1

when the FIFO level is equal to or less than

this threshold.

8

ALMOST_FULL2_THRESHOLD

RW

0

Secondary almost-full threshold. The bit

Almost_full_data[1]

on the Avalon-ST

almost-full status interface is set to 1 when

the FIFO level is equal to or greater than

this threshold.

12

ALMOST_EMPTY2_

THRESHOLD

RW

0

Secondary almost-empty threshold. The bit

Almost_empty_data[1]

on the Avalon-ST

almost-empty status interface is set to 1

when the FIFO level is equal to or less than

this threshold.

Base

+ 8

Almost_Empty_Threshold

RW

The value of the primary almost-empty

threshold. The bit

Almost_empty_data

[0]

on the Avalon-ST almost-empty status

interface is set to 1 when the FIFO level is

greater than or equal to this threshold.

Base

+ 12

Almost_Empty2_Threshold

RW

The value of the secondary almost-empty

threshold. The bit

Almost_empty_data

[1]

Avalon-ST almost-empty status interface is

set to 1 when the FIFO level is greater than

or equal to this threshold.

Fill-Level Register Interface

The table below shows the register map for the fill-level interface.

UG-01085

2014.24.07

Register Map

17-7

Avalon-ST Multi-Channel Shared Memory FIFO Core

Altera Corporation