Software files, Register map, Software files -6 – Altera Embedded Peripherals IP User Manual

Page 237: Register map -6

Request

Meaning

1. These macro names changed in version 1.1 of the Nios II Embedded Design Suite (EDS). The

old names (

ALT_DMA_TX_STREAM_ON

,

ALT_DMA_TX_STREAM_OFF

,

ALT_DMA_RX_STREAM_ON

, and

ALT_DMA_RX_STREAM_OFF)

are still valid, but new designs should use the new names.

Limitations

Currently the Altera-provided drivers do not support 64-bit and 128-bit DMA transactions.

This function is not thread safe. If you want to access the DMA controller from more than one thread

then you should use a semaphore or mutex to ensure that only one thread is executing within this

function at any time.

Software Files

The DMA controller is accompanied by the following software files. These files define the low-level

interface to the hardware. Application developers should not modify these files.

•

altera_avalon_dma_regs.h

—This file defines the core’s register map, providing symbolic constants to

access the low-level hardware. The symbols in this file are used only by device driver functions.

•

altera_avalon_dma.h

,

altera_avalon_dma.c

—These files implement the DMA controller’s device driver for

the HAL system library.

Register Map

Programmers using the HAL API never access the DMA controller hardware directly via its registers. In

general, the register map is only useful to programmers writing a device driver.

The Altera-provided HAL device driver accesses the device registers directly. If you are writing a device

driver, and the HAL driver is active for the same device, your driver will conflict and fail to operate.

Device drivers control and communicate with the hardware through five memory-mapped 32-bit

registers.

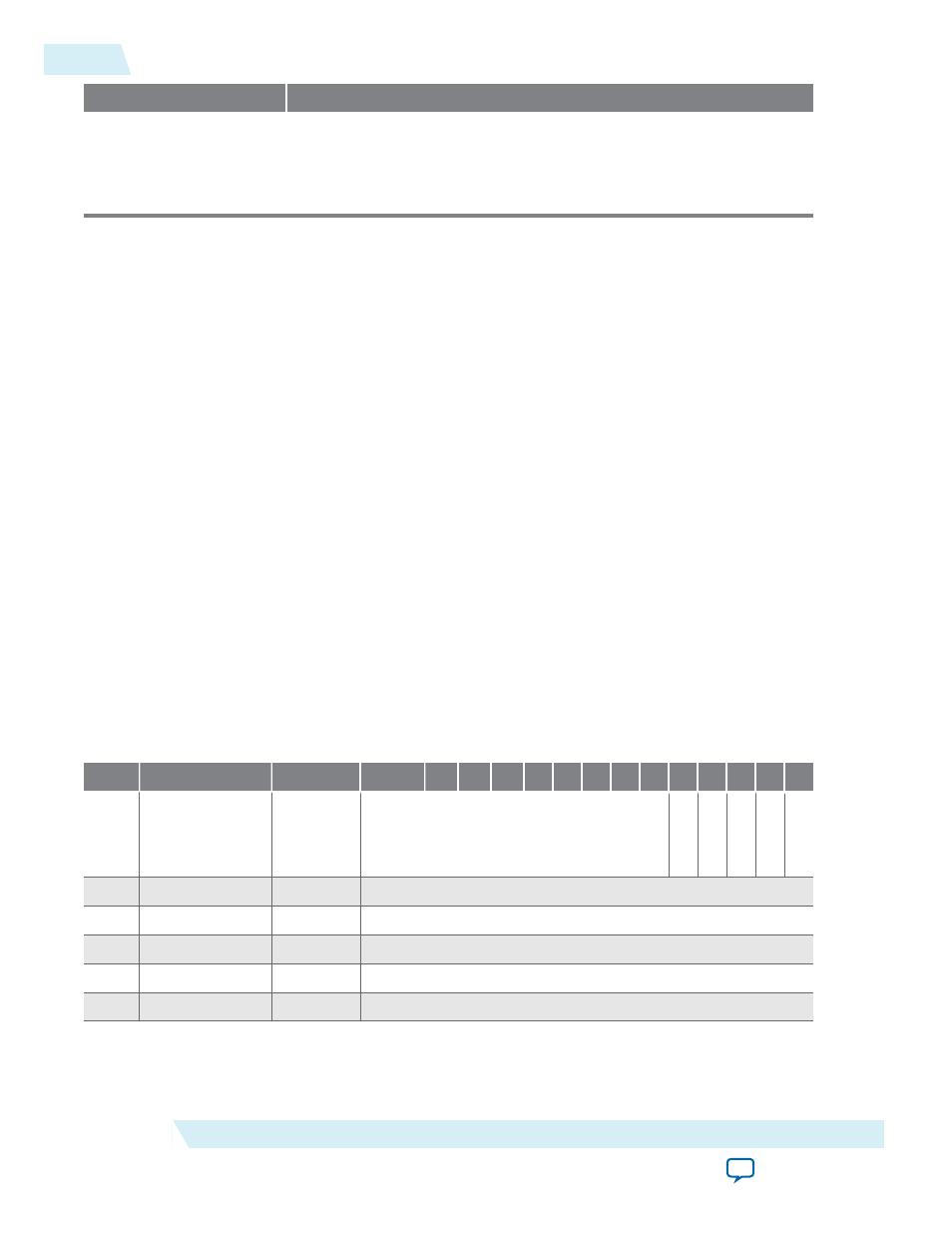

Table 23-3: DMA Controller Register Map

Offset

Register Name

Read/Write

31 13

12 11 10 9

8

7

6

5

4

3

2

1

0

0

status

RW

LE

N

WE

OP

RE

OP

BU

SY

D

O

N

E

1

readaddress

RW

Read master start address

2

writeaddress

RW

Write master start address

3

length

RW

DMA transaction length (in bytes)

4

—

—

5

—

—

23-6

Software Files

UG-01085

2014.24.07

Altera Corporation

DMA Controller Core