Altera Embedded Peripherals IP User Manual

Page 82

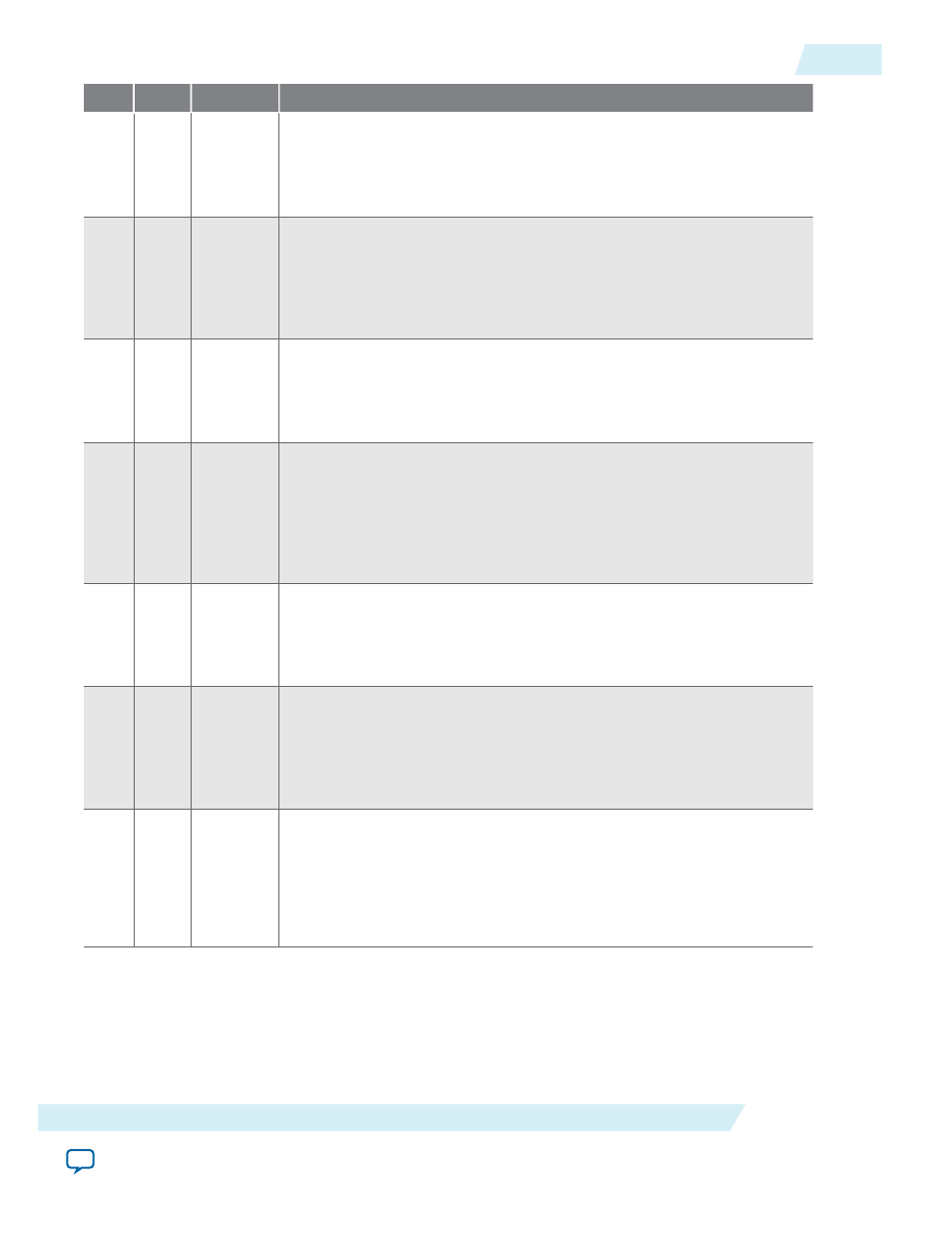

Bit

Name

Access

Description

2

BRK

RC

Break detect. The receiver logic detects a break when the

RXD

pin is held

low (logic 0) continuously for longer than a full-character time (data

bits, plus start, stop, and parity bits). When a break is detected, the

BRK

bit is set to 1. The

BRK

bit stays set to 1 until it is explicitly cleared by a

write to the

status

register.

3

ROE

RC

Receive overrun error. A receive-overrun error occurs when a newly

received character is transferred into the

rxdata

holding register before

the previous character is read (in other words, while the

RRDY

bit is 1). In

this case, the

ROE

bit is set to 1, and the previous contents of

rxdata

are

overwritten with the new character. The

ROE

bit stays set to 1 until it is

explicitly cleared by a write to the

status

register.

4

TOE

RC

Transmit overrun error. A transmit-overrun error occurs when a new

character is written to the

txdata

holding register before the previous

character is transferred into the shift register (in other words, while the

TRDY

bit is 0). In this case the

TOE

bit is set to 1. The

TOE

bit stays set to 1

until it is explicitly cleared by a write to the

status

register.

5

TMT

R

Transmit empty. The

TMT

bit indicates the transmitter shift register’s

current state. When the shift register is in the process of shifting a

character out the

TXD

pin,

TMT

is set to 0. When the shift register is idle

(in other words, a character is not being transmitted) the

TMT

bit is 1. An

Avalon-MM master peripheral can determine if a transmission is

completed (and received at the other end of a serial link) by checking the

TMT

bit.

6

TRDY

R

Transmit ready. The

TRDY

bit indicates the

txdata

holding register’s

current state. When the

txdata

register is empty, it is ready for a new

character, and

TRDY

is 1. When the

txdata

register is full,

TRDY

is 0. An

Avalon-MM master peripheral must wait for

TRDY

to be 1 before writing

new data to

txdata

.

7

RRDY

R

Receive character ready. The

RRDY

bit indicates the

rxdata

holding

register’s current state. When the

rxdata

register is empty, it is not ready

to be read and

RRDY

is 0. When a newly received value is transferred into

the

rxdata

register,

RRDY

is set to 1. Reading the

rxdata

register clears

the

RRDY

bit to 0. An Avalon-MM master peripheral must wait for

RRDY

to equal 1 before reading the

rxdata

register.

8

E

RC

Exception. The

E

bit indicates that an exception condition occurred. The

E

bit is a logical-OR of the

TOE

,

ROE

,

BRK

,

FE

, and

PE

bits. The

E

bit and its

corresponding interrupt-enable bit (

IE

) bit in the

control

register

provide a convenient method to enable/disable IRQs for all error

conditions.

The

E

bit is set to 0 by a write operation to the

status

register.

UG-01085

2014.24.07

status Register

8-13

UART Core

Altera Corporation