Driver examples, Driver examples -16 – Altera Embedded Peripherals IP User Manual

Page 102

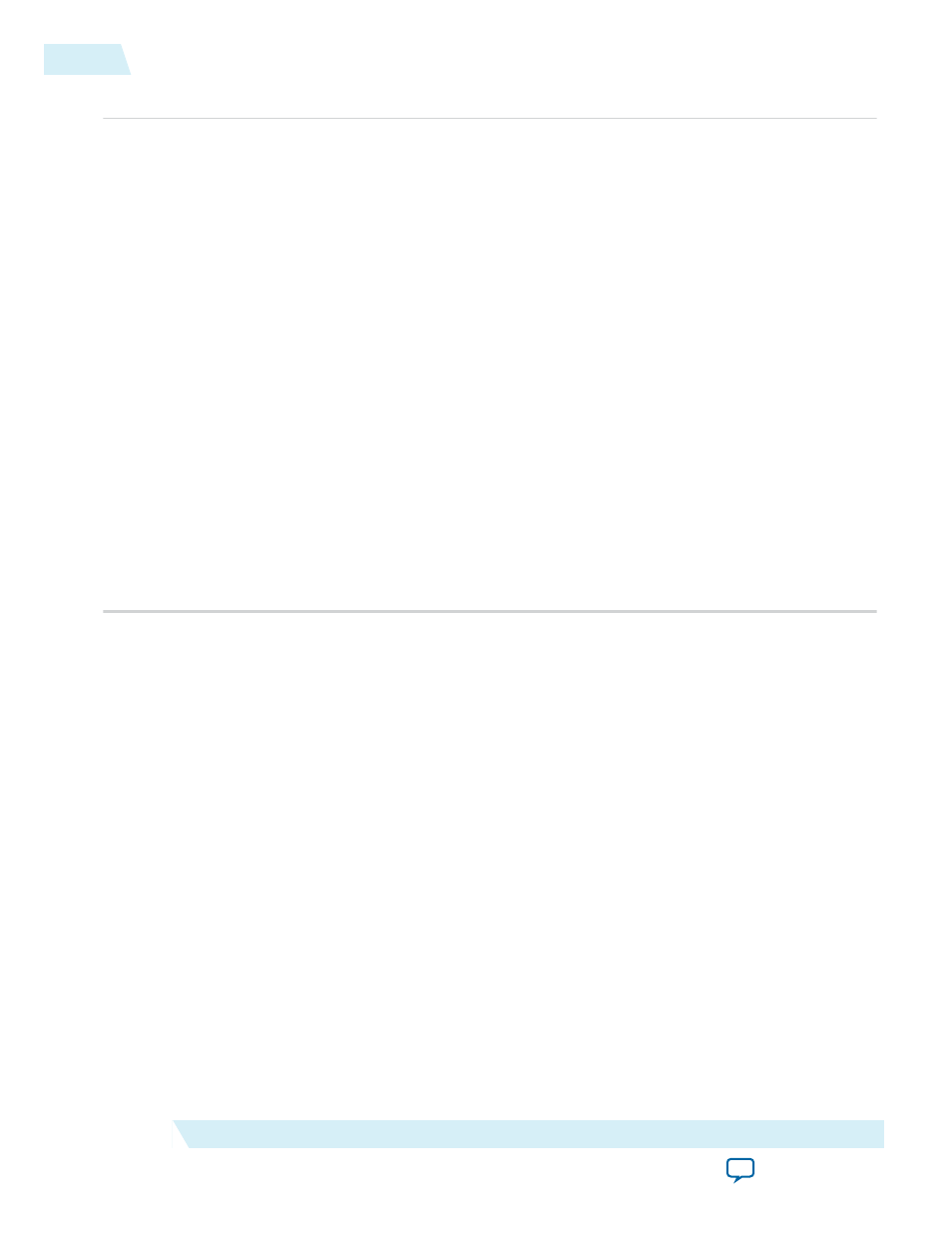

Figure 9-8:

typedef

struct altera_16550_uart_state_s

{

alt_dev

dev;

void*

base;

/* The base address of the device */

alt_u32

clock;

alt_u32

FIFOMode

alt_u32

ctrl;

/* Shadow value of the LSR register */

alt_u32

rx_start;

/* Start of the pending receive data*/

volatile alt_u32

rx_end;

/* End of the pending receive data */

volatile alt_u32

tx_start;

/* Start of the pending transmitdata*/

alt_u32

tx_end;

/* End ofthe pending transmit data */

alt_u32

freq;

/* Current clock freq rate */

UartConfig

config;

/* Uart setting */

alt_u32

flags;

/* Configuration flags */

ALT_FLAG_GRP (events)

/* Event flags used for

* foreground/background in mult-

*threaded mode*/

ALT_SEM

(read_lock)

/* Semaphore used to control access

* to the read buffer in multi-

*threaded mode*/

ALT_SEM

(write_lock)

/* Semaphore used to control access

* to the write buffer in multi-

*threaded mode */

alt_u8 rx_buf[ALT_16550_UART_BUF_LEN];

/* The receive buffer */

alt_u8 tx_buf[ALT_16550_UART_BUF_LEN];

/* The transmit buffer */

} altera_16550_uart_state;

Driver Examples

Below is a simple test program to verify that the Altera 16550 UART driver support is functional.

The test reads, validates, and writes a modified baud rate, data bits, stop bits, parity bits to the UART

before attempting to write a character stream to it from UART0 to UART1 and vice verse (ping pong

test). This also tests the FIFO and FIFO-less mode as well as the HW flow control to ensure the IP is

functioning for FIFO and HWFC.

Prerequisites needed before running test:

• An instance of UART named "uart0" and another instance UART named "uart1"

• Both UARTs need to be connected in loopback in Quartus.

Additional coverage:

• Non-blocking UART support

• UART HAL driver

• HAL open/write support

The test will print "PASS: . . ." from the UART to indicate success.

#include

#include

#include

#include

#include

#include

9-16

Driver Examples

UG-01085

2014.24.07

Altera Corporation

16550 UART