Receiver logic, Master and slave modes, Receiver logic -3 – Altera Embedded Peripherals IP User Manual

Page 109: Master and slave modes -3

from 8 to 32. After a master peripheral writes a value to the

txdata

register, the value is copied to the shift

register and then transmitted when the next operation starts.

The shift register and the

txdata

register provide double buffering during data transmission. A new value

can be written into the

txdata

register while the previous data is being shifted out of the shift register.

The transmitter logic automatically transfers the

txdata

register to the shift register whenever a serial

shift operation is not currently in process.

In master mode, the transmit shift register directly feeds the

mosi

output. In slave mode, the transmit shift

register directly feeds the

miso

output. Data shifts out LSB first or MSB first, depending on the configura‐

tion of the SPI core.

Receiver Logic

The SPI core receive logic consists of a receive holding register (

rxdata

) and receive shift register, each n

bits wide. The register width n is specified at system generation time, and can be any integer value from 8

to 32. A master peripheral reads received data from the

rxdata

register after the shift register has captured

a full n-bit value of data.

The shift register and the

rxdata

register provide double buffering while receiving data. The

rxdata

register can hold a previously received data value while subsequent new data is shifting into the shift

register. The receiver logic automatically transfers the shift register content to the

rxdata

register when a

serial shift operation completes.

In master mode, the shift register is fed directly by the

miso

input. In slave mode, the shift register is fed

directly by the

mosi

input. The receiver logic expects input data to arrive LSB first or MSB first, depending

on the configuration of the SPI core.

Master and Slave Modes

At system generation time, the designer configures the SPI core in either master mode or slave mode. The

mode cannot be switched at runtime.

Master and Slave Modes

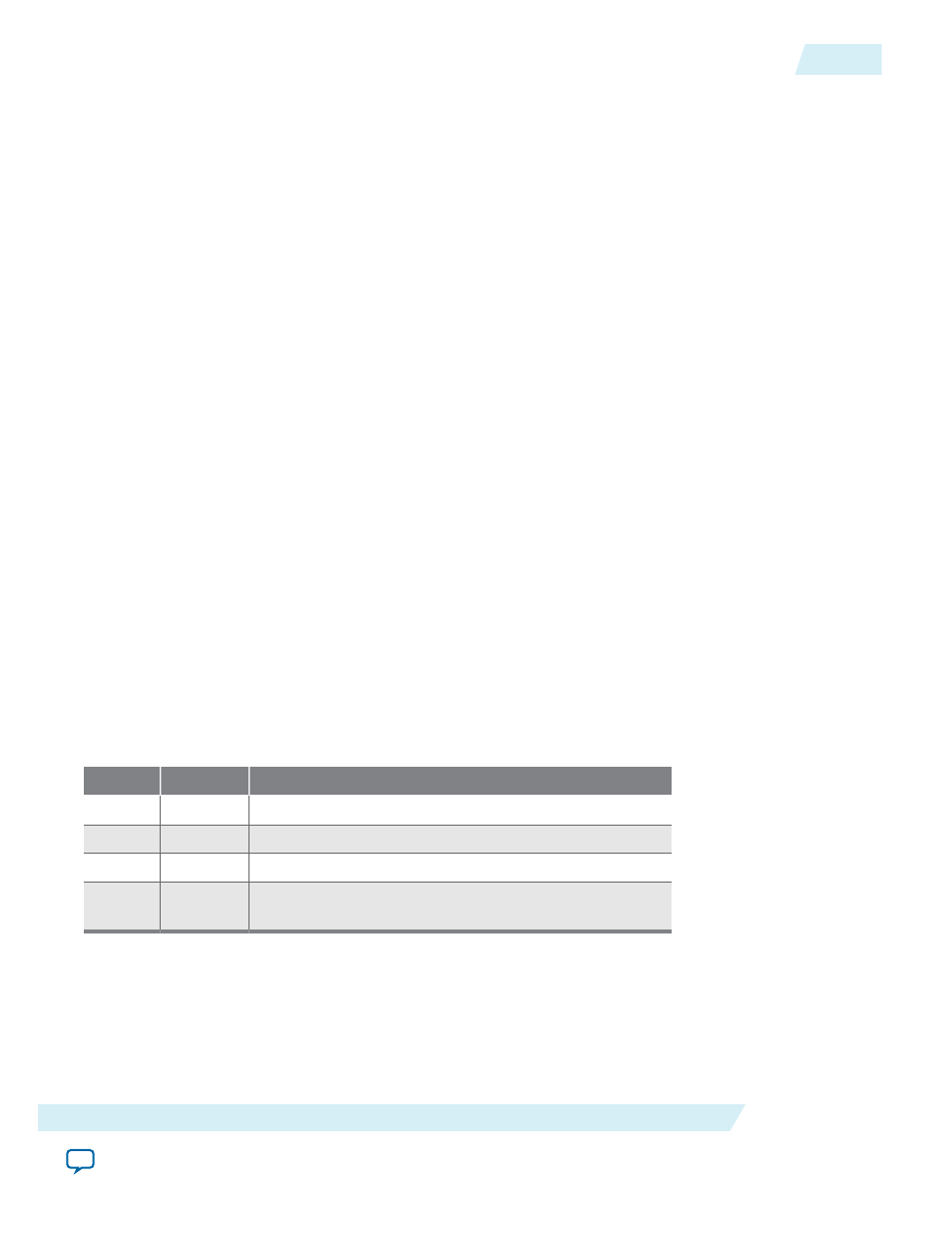

In master mode, the SPI ports behave as shown in the table below.

Table 10-1: Master Mode Port Configurations

Name

Direction

Description

mosi

output

Data output to slave(s)

miso

input

Data input from slave(s)

sclk

output

Synchronization clock to all slaves

ss_

n

M

output

Slave select signal to slave M, where M is a number

between 0 and 31.

In master mode, an intelligent host (for example, a microprocessor) configures the SPI core using the

control

and

slaveselect

registers, and then writes data to the

txdata

buffer to initiate a transaction. A

master peripheral can monitor the status of the transaction by reading the

status

register. A master

peripheral can enable interrupts to notify the host whenever new data is received (for example, a transfer

has completed), or whenever the transmit buffer is ready for new data.

The SPI protocol is full duplex, so every transaction both sends and receives data at the same time. The

master transmits a new data bit on the

mosi

output and the slave drives a new data bit on the

miso

input

UG-01085

2014.24.07

Receiver Logic

10-3

SPI Core

Altera Corporation