Software programming model, Hal system library support, Register map – Altera Embedded Peripherals IP User Manual

Page 179: Software programming model -6, Hal system library support -6, Register map -6

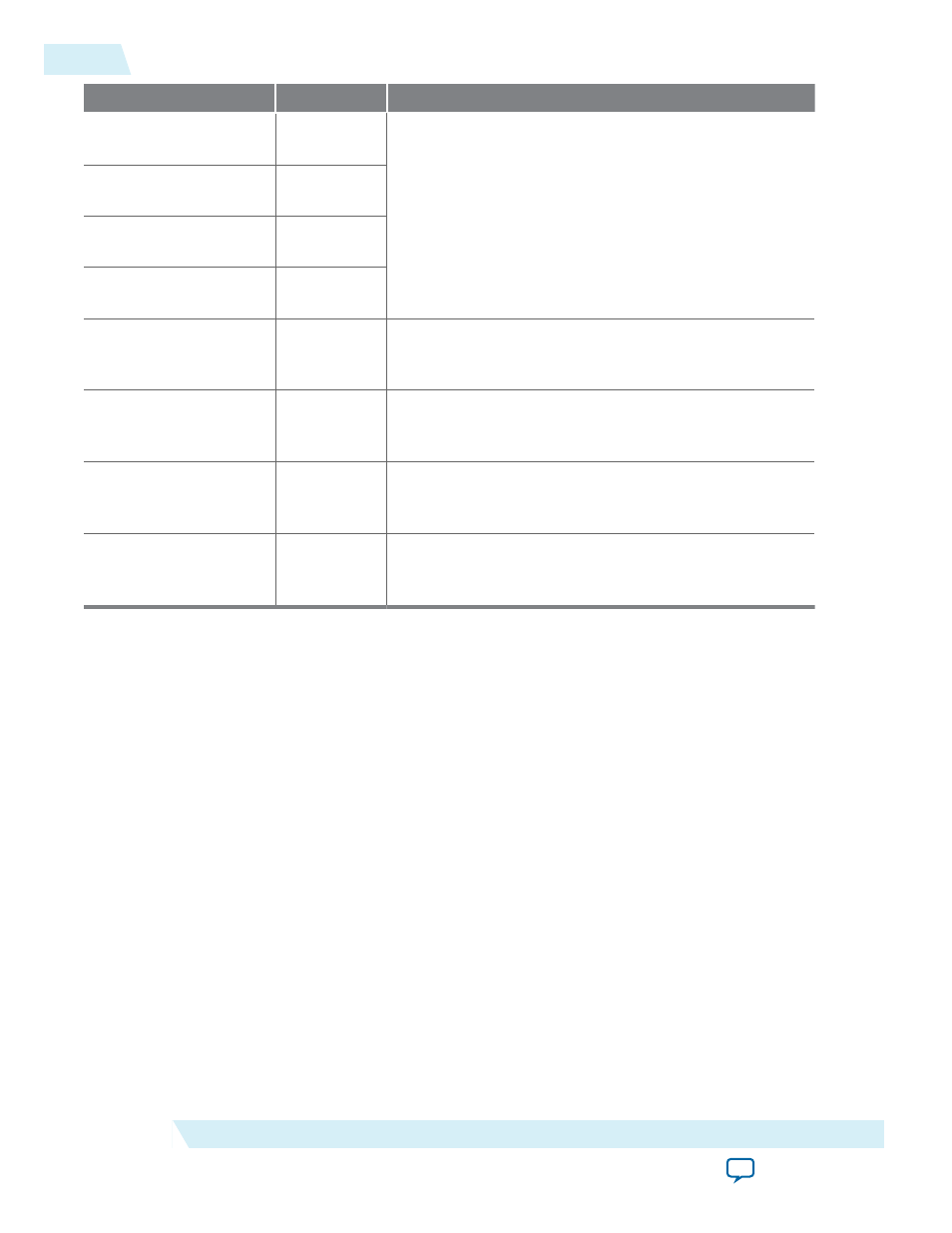

Parameter

Legal Values

Description

Use almost-full

threshold 1

—

Turn on these parameters to implement the optional

Avalon-ST almost-full and almost-empty interfaces and

their corresponding registers. See Control Interface

Register Map for the description of the threshold

registers.

Use almost-full

threshold 2

—

Use almost-empty

threshold 1

—

Use almost-empty

threshold 2

—

Use almost-full

threshold 1

0 or 1

This threshold indicates that the FIFO is almost full. It is

enabled when the parameter Number of almost-full

threshold is set to 1 or 2.

Use almost-full

threshold 2

0 or 1

This threshold is an initial indication that the FIFO is

getting full. It is enabled when the parameter Number of

almost-full threshold is set to 2.

Use almost-empty

threshold 1

0 or 1

This threshold indicates that the FIFO is almost empty. It

is enabled when the parameter Number of almost-

empty threshold is set to 1 or 2.

Use almost-empty

threshold 2

0 or 1

This threshold is an initial indication that the FIFO is

getting empty. It is enabled when the parameter Number

of almost-empty threshold is set to 2.

Software Programming Model

The following sections describe the software programming model for the Avalon-ST Multi-Channel

Shared FIFO core.

HAL System Library Support

The Altera-provided driver implements a HAL device driver that integrates into the HAL system library

for Nios II systems. HAL users should access the Avalon-ST Multi-Channel Shared FIFO core via the

familiar HAL API and the ANSI C standard library.

Register Map

You can configure the thresholds and retrieve the fill-level for each channel via the Avalon-MM control

and fill-level interfaces respectively. Subsequent sections describe the registers accessible via each

interface.

17-6

Software Programming Model

UG-01085

2014.24.07

Altera Corporation

Avalon-ST Multi-Channel Shared Memory FIFO Core