Functional description, Altpll megafunction, Clock outputs – Altera Embedded Peripherals IP User Manual

Page 313: Pll status and control signals, Functional description -2, Altpll megafunction -2, Clock outputs -2, Pll status and control signals -2, Figure 32-1: pll core block diagram

Functional Description

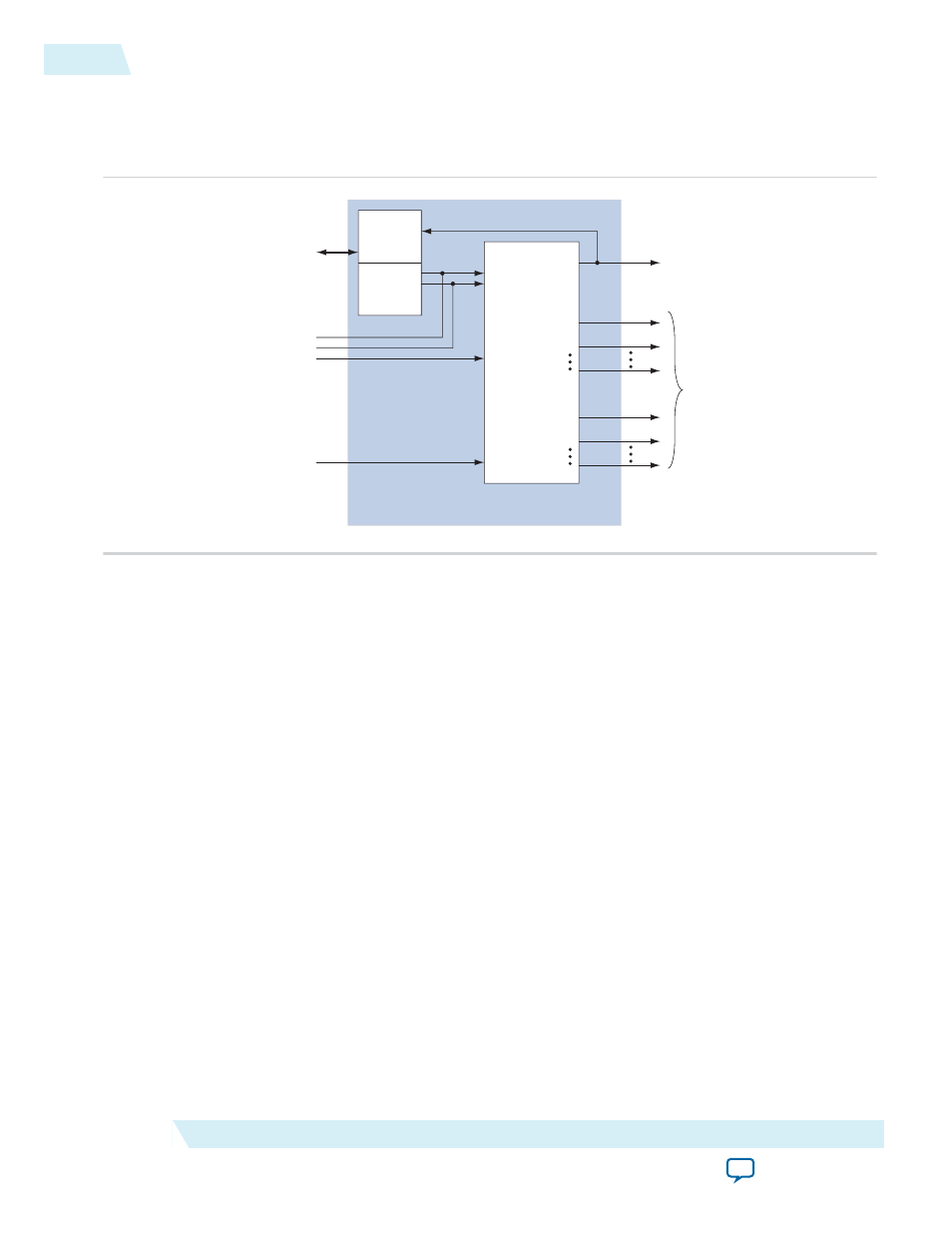

Figure 32-1: PLL Core Block Diagram

Status

Control

areset

pfdena

pllena

inclk

e1

e0

c1

c0

locked

PLL Locked

Avalon-MM

Slave Interface

PLL Reset

PFD Ena

ble

PLL Ena

ble

Reference

Clock

Registers

PLL Co

re

ALTPLL Megafunc

tion

PLL Clo

ck

Outputs

ALTPLL Megafunction

The PLL cores consist of an ALTPLL megafunction instantiation and an Avalon-MM slave interface. This

interface can optionally provide access to status and control registers within the cores. The ALTPLL

megafunction takes an SOPC Builder system clock as its reference, and generates one or more phase-

locked loop output clocks.

Clock Outputs

Depending on the target device family, the ALTPLL megafunction can produce two types of output clock:

• internal (c)—clock outputs that can drive logic either inside or outside the SOPC Builder system

module. Internal clock outputs can also be mapped to top-level FPGA pins. Internal clock outputs are

available on all device families.

• external (e)—clock outputs that can only drive dedicated FPGA pins. They cannot be used as on-chip

clock sources. External clock outputs are not available on all device families.

The Avalon ALTPLL core, however, does not differentiate the internal and external clock outputs and

allows the external clock outputs to be used as on-chip clock sources.

To determine the exact number and type of output clocks available on your target device, refer to the

PLL Status and Control Signals

Depending on how the ALTPLL megafunction is parameterized, there can be a variable number of status

and control signals. You can choose to export certain status and control signals to the top-level SOPC

Builder system module. Alternatively, Avalon-MM registers can provide access to the signals. Any status

32-2

Functional Description

UG-01085

2014.24.07

Altera Corporation

PLL Cores