Timeouts, Timeouts -15 – Altera Embedded Peripherals IP User Manual

Page 206

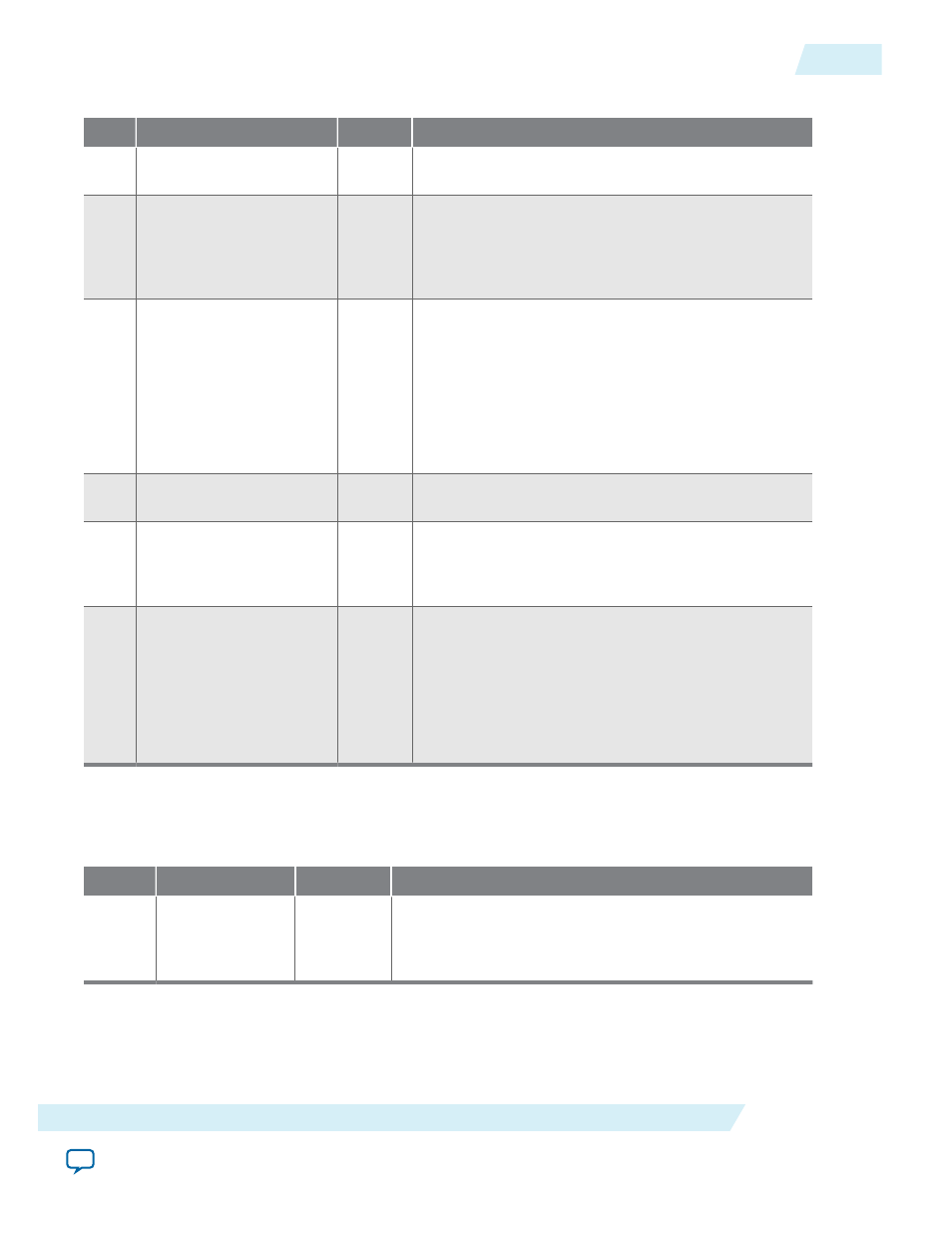

Table 21-11: DESC_CONTROL Bit Map

Bit (s)

Field Name

Access

Description

0

GENERATE_EOP

W

When this bit is set to 1,the DMA read block asserts

the EOP signal on the final word.

1

READ_FIXED_ADDRESS

R/W

This bit applies only to Avalon-MM read master

ports. When this bit is set to 1, the DMA read block

does not increment the memory address. When this

bit is set to 0, the read address increments after each

read.

2

WRITE_FIXED_ADDRESS

R/W

This bit applies only to Avalon-MM write master

ports. When this bit is set to 1, the DMA write block

does not increment the memory address. When this

bit is set to 0, the write address increments after each

write.

In memory-to-stream configurations, the DMA read

block generates a start-of-packet (SOP) on the first

word when this bit is set to 1.

[6:

3]

Reserved

—

—

3 .

. 6

AVALON-ST_CHANNEL_

NUMBER

R/W

The DMA read block sets the

channel

signal to this

value for each word in the transaction. The DMA

write block replaces this value with the channel

number on its sink port.

7

OWNED_BY_HW

R/W

This bit determines whether hardware or software

has write access to the current register.

When this bit is set to 1, the core can update the

descriptor and software should not access the

descriptor due to the possibility of race conditions.

Otherwise, it is safe for software to update the

descriptor.

After completing a DMA transaction, the descriptor processor block updates the

desc_status

field to

indicate how the transaction proceeded.

Table 21-12: DESC_STATUS Bit Map

Bit

Bit Name

Access

Description

[7:0]

ERROR_0

..

ERROR_

7

R

Each bit represents an error that occurred on the

Avalon-ST interface. The context of each error is

defined by the component connected to the Avalon-ST

interface.

Timeouts

The SG-DMA controller does not implement internal counters to detect stalls. Software can instantiate a

timer component if this functionality is required.

UG-01085

2014.24.07

Timeouts

21-15

Scatter-Gather DMA Controller Core

Altera Corporation