Component interface, Component parameterization, Component interface -7 – Altera Embedded Peripherals IP User Manual

Page 326: Component parameterization -7

Component Interface

The Altera MSI-to-GIC Generator component consists of two Avalon-MM Slave interfaces, CSR and Data

storage. The component also provides active high level interrupt output, which is served as a message

arrival notification to the host processor.

The Altera MSI-to-GIC Generator has only one clock domain with one associated reset interface. The

requirement of different clock domains between the host processor and the PCIe HIP is handled by the

Qsys fabric.

The following table describes the interfaces behavior of the component.

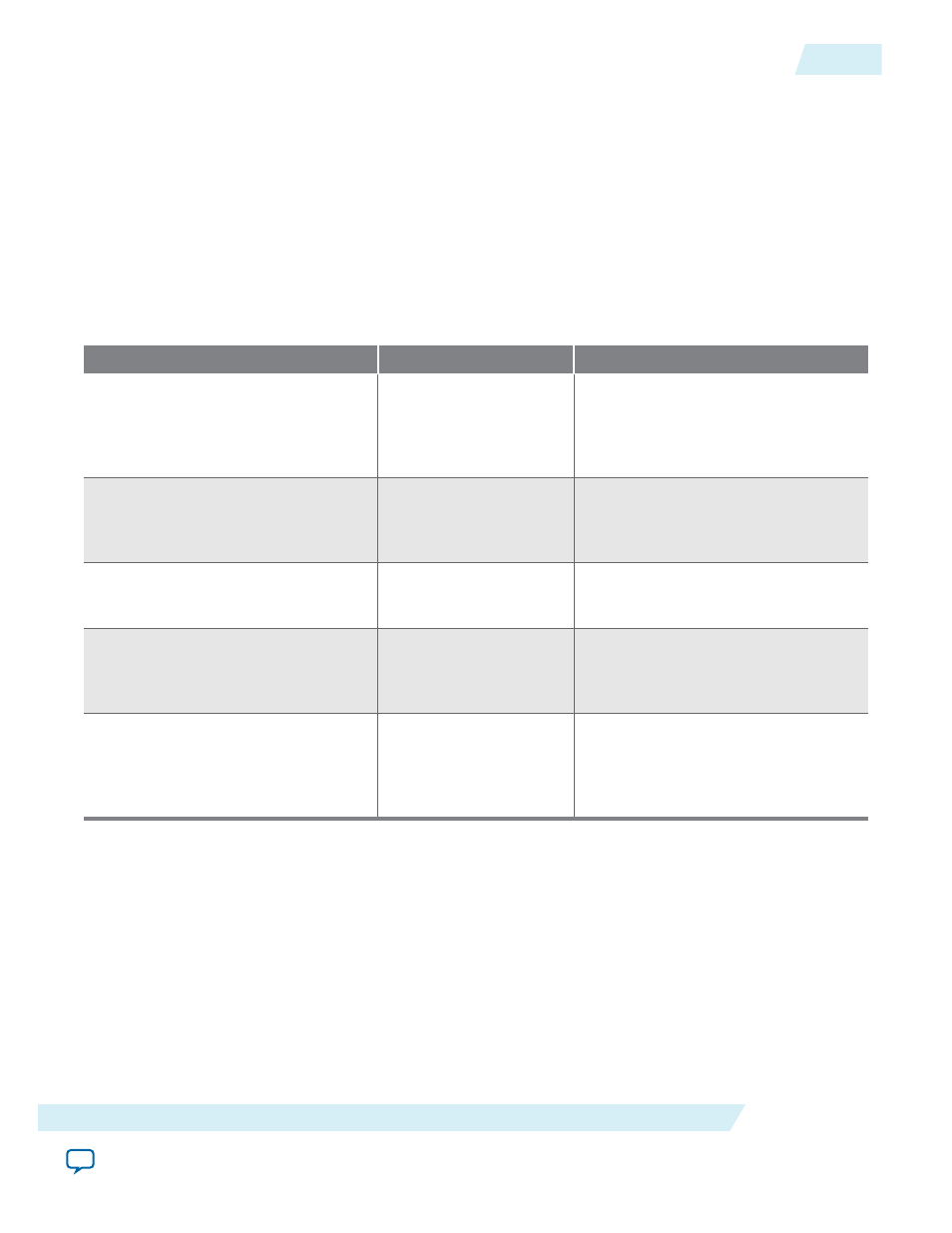

Table 33-9: Component interfaces

Interface Port

Description

Remarks

Avalon MM Slave (Data storage)

The Avalon-MM Slave

interface for the Master

that writes MSI message

data to the memory

location.

This interface follows the protocol of

the fix latency of one cycle. Every

single write is consumed in the next

cycle. No back pressure can happen.

Avalon MM Slave (CSR)

The Avalon-MM Slave

interface for the host

processor servicing the

MSI.

This interface only has a write latency

of one cycle and a read latency of one

cycle.

Clock

Clock input of component. This interface supports maximum

frequency up to 200MHz on Cyclone

V and 350MHz on Stratix V devices.

Reset_n

Active LOW reset input.

This interface supports asynchronous

reset assertion. De-assertion of reset

has to be synchronized to the input

clock.

IRQ

Interrupt output

This interface sends an interrupt

output to the host processor. Any

asserted Status bit with associated

Masking bit de-asserted causes the

interrupt to output high.

Component Parameterization

UG-01085

2014.24.07

Component Interface

33-7

Altera MSI to GIC Generator

Altera Corporation