Hardware simulation considerations, Document revision history, Hardware simulation considerations -6 – Altera Embedded Peripherals IP User Manual

Page 247: Document revision history -6

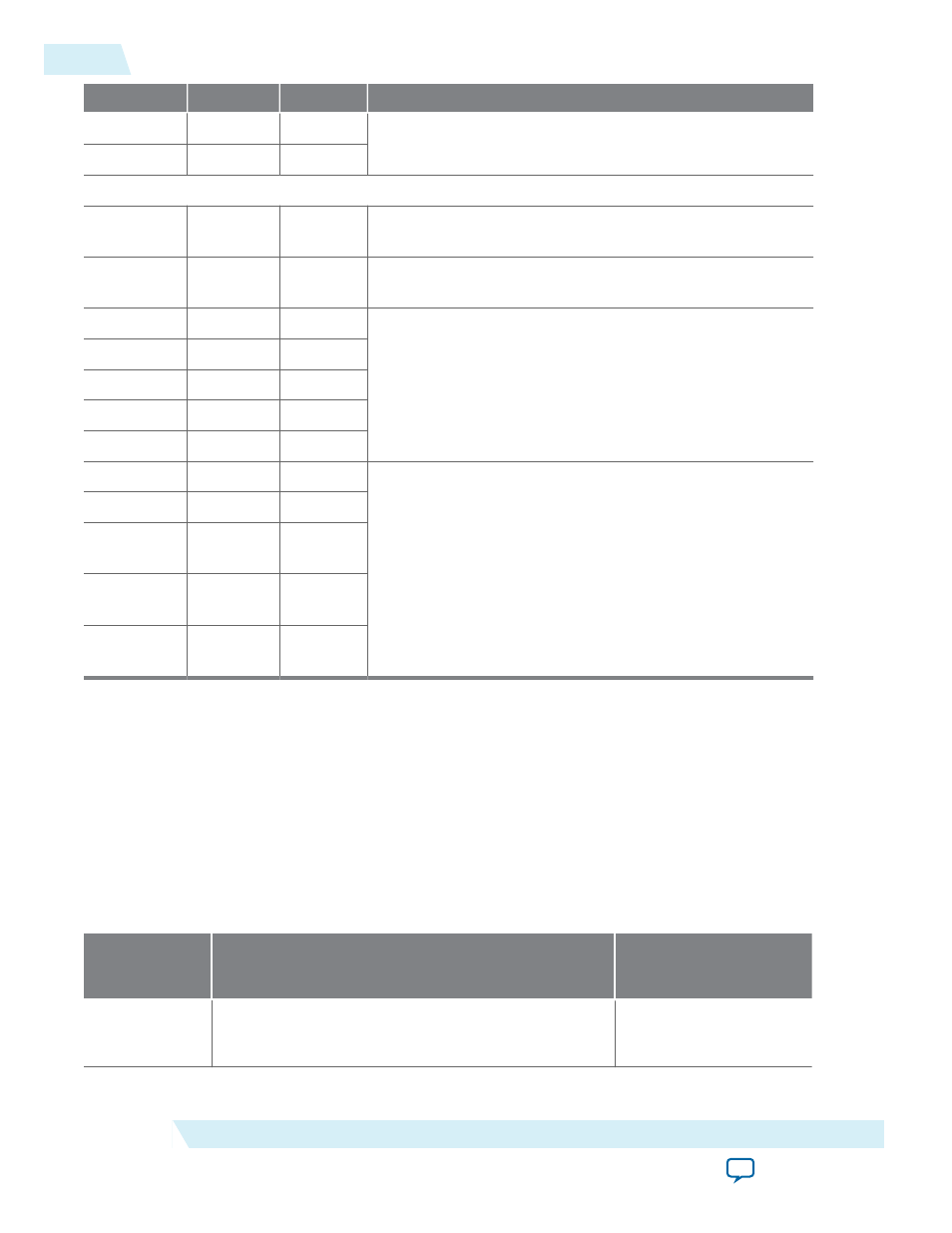

Signal Name Width (Bits)

Direction

Description

clk

1

Input

Not in use.

reset_n

1

Input

Avalon-ST Signals

data_in

32

Input

Incoming pixel data. Contains four 8-bit symbols that are

transferred in 1 beat.

data_out

24

Output

Output data. Contains three 8-bit symbols that are

transferred in 1 beat.

sop_in

1

Input

Wired directly to the corresponding output signals.

eop_in

1

Input

ready_in

1

Input

valid_in

1

Input

empty_in

1

Input

sop_out

1

Output

Wired directly from the input signals.

eop_out

1

Output

ready_

out

1

Output

valid_

out

1

Output

empty_

out

1

Output

Hardware Simulation Considerations

For a typical 60 Hz refresh rate, set the simulation length for the video sync generator core to at least 16.7

μs to get a full video frame. Depending on the size of the video frame, simulation may take a very long

time to complete.

Document Revision History

Table 24-4: Document Revision History

Date and

Document

Version

Changes Made

Summary of Changes

July 2014

v14.0.0

-Removed mention of SOPC Builder, updated to Qsys

Maintenance Release

24-6

Hardware Simulation Considerations

UG-01085

2014.24.07

Altera Corporation

Video Sync Generator and Pixel Converter Cores