Altera Embedded Peripherals IP User Manual

Page 202

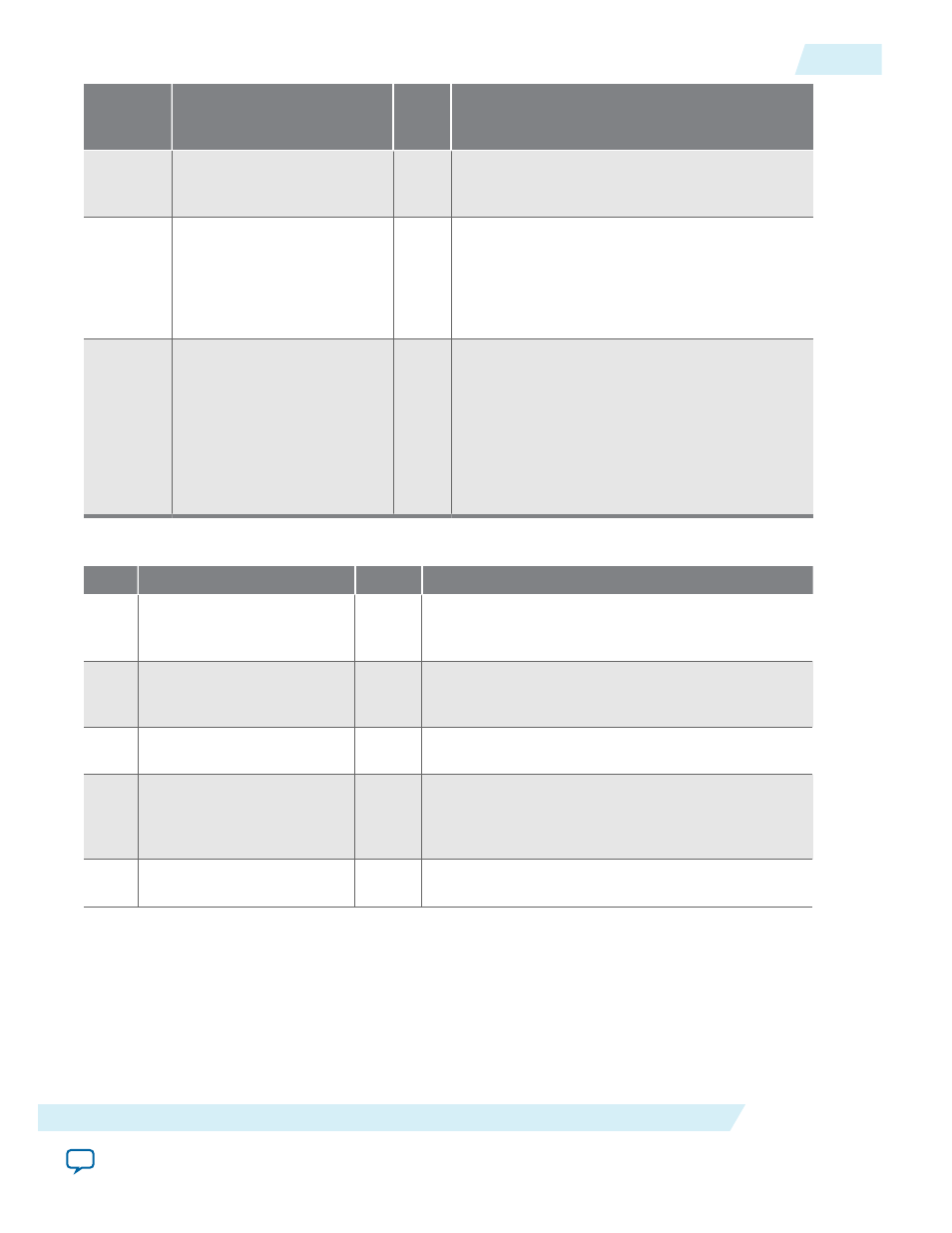

32-bit

Word

Offset

Register Name

Reset

Value

Description

base +

1

version

1

Indicate the hardware version number. Only

being used by software driver for software

backward compatibility purpose.

base +

4

control

0

This register specifies the core’s behavior such

as what triggers an interrupt and when the core

is started and stopped. The host processor can

configure the core by setting the register bits

accordingly. See the Control Register Bit Map

table for the

control

register map.

base +

8

next_descriptor_pointer

0

This register contains the address of the next

descriptor to process. Set this register to the

address of the first descriptor as part of the

system initialization sequence.

Altera recommends that user applications clear

the

RUN

bit in the

control

register and wait

until the

BUSY

bit of the

status

register is set to

0 before reading this register.

Table 21-7: Control Register Bit Map

Bit

Bit Name

Access

Description

0

IE_ERROR

R/W

When this bit is set to 1, the core generates an

interrupt if an Avalon-ST error occurs during

descriptor processing.

1

IE_EOP_ENCOUNTERED

R/W

When this bit is set to 1, the core generates an

interrupt if an EOP is encountered during

descriptor processing.

2

IE_DESCRIPTOR_COMPLETED

R/W

When this bit is set to 1, the core generates an

interrupt after each descriptor is processed.

3

IE_CHAIN_COMPLETED

R/W

When this bit is set to 1, the core generates an

interrupt after the last descriptor in the list is

processed, that is when the core encounters a

descriptor with a cleared

OWNED_BY_HW

bit.

4

IE_GLOBAL

R/W

When this bit is set to 1, the core is enabled to

generate interrupts.

UG-01085

2014.24.07

Register Maps

21-11

Scatter-Gather DMA Controller Core

Altera Corporation