On-chip fifo memory api, Altera_avalon_fifo_init(), Altera_avalon_fifo_read_status() – Altera Embedded Peripherals IP User Manual

Page 167: On-chip fifo memory api -12, Altera_avalon_fifo_init() -12, Altera_avalon_fifo_read_status() -12

void* input_fifo_wrclk_irq_event_ptr = (void*) &input_fifo_wrclk_irq_event;

/* Enable all interrupts. */

/* Clear event register, set enable all irq, set almostempty and

almostfull threshold */

return_code = altera_avalon_fifo_init(INPUT_FIFO_IN_CSR_BASE,

0, // Disabled interrupts

ALMOST_EMPTY,

ALMOST_FULL);

/* Register the interrupt handler. */

alt_irq_register( INPUT_FIFO_IN_CSR_IRQ,

input_fifo_wrclk_irq_event_ptr, handle_input_fifo_wrclk_interrupts );

return return_code;

}

On-Chip FIFO Memory API

This section describes the application programming interface (API) for the on-chip FIFO memory core.

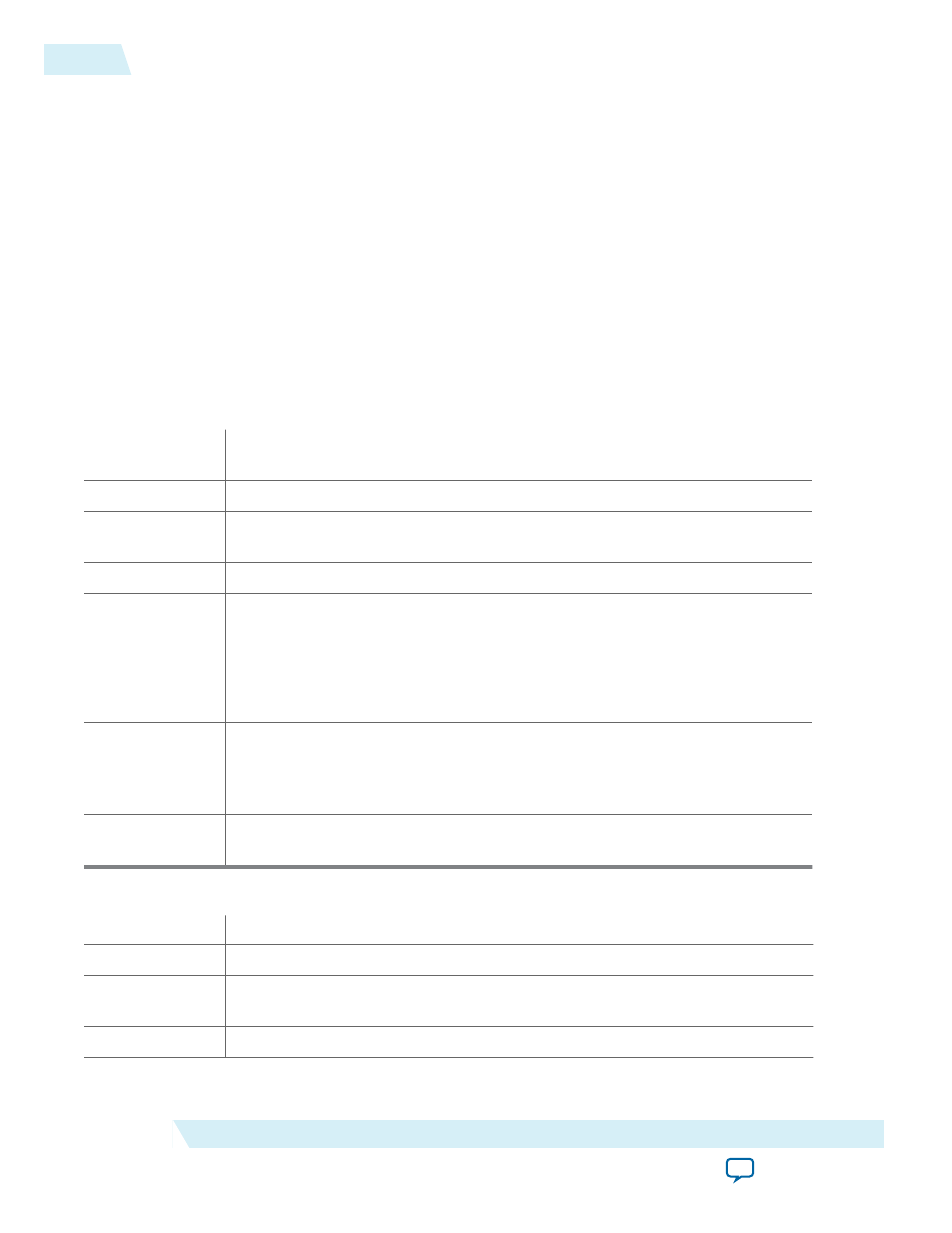

altera_avalon_fifo_init()

Prototype:

int altera_avalon_fifo_init(alt_u32 address, alt_u32 ienable, alt_

u32 emptymark, alt_u32 fullmark)

Thread-safe:

No.

Available from

ISR:

No.

Include:

<altera_avalon_fifo_regs.h>, <altera_avalon_fifo_utils.h>

Parameters:

address

—the base address of the FIFO control slave

ienable

—the value to write to the

interruptenable

register

emptymark

—the value for the almost empty threshold level

fullmark

—the value for the almost full threshold level

Returns:

Returns 0 (

ALTERA_AVALON_FIFO_OK

) if successful,

ALTERA_AVALON_FIFO_

EVENT_CLEAR_ERROR

for clear errors,

ALTERA_AVALON_FIFO_IENABLE_WRITE_

ERROR

for interrupt enable write errors,

ALTERA_AVALON_FIFO_THRESHOLD_

WRITE_ERROR

for errors writing the

almostfull

and

almostempty

registers.

Description:

Clears the

event

register, writes the

interruptenable

register, and sets the

almostfull

register and

almostempty

registers.

altera_avalon_fifo_read_status()

Prototype:

int altera_avalon_fifo_read_status(alt_u32 address, alt_u32 mask)

Thread-safe:

No.

Available from

ISR:

No.

Include:

<altera_avalon_fifo_regs.h>, <altera_avalon_fifo_utils.h>

16-12

On-Chip FIFO Memory API

UG-01085

2014.24.07

Altera Corporation

On-Chip FIFO Memory Core