Register map, Rxdata register, Txdata register – Altera Embedded Peripherals IP User Manual

Page 115: Register map -9

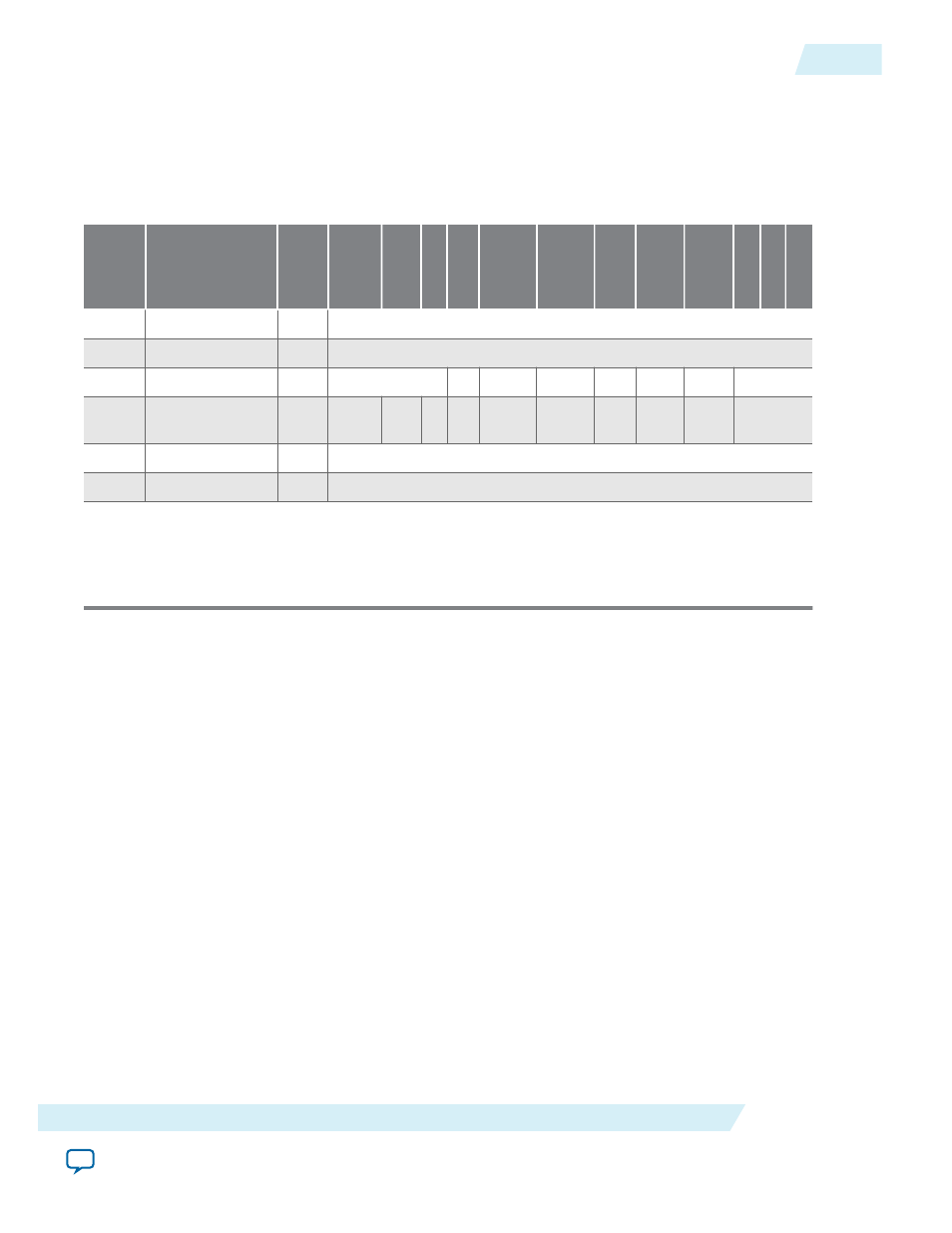

Register Map

An Avalon-MM master peripheral controls and communicates with the SPI core via the six 32-bit

registers, shown in below in the Register Map for SPI Master Device figure. The table assumes an n-bit

data width for

rxdata

and

txdata

.

Table 10-5: Register Map for SPI Master Device

Interna

l

Addres

s

Register Name

Type

[R/W]

32..11 10

9

8

7

6

5

4

3

2 1 0

0

rxdata

R

RXDATA

(n-1..0)

1

txdata

W

TXDATA

(n-1..0)

2

status

R/W

E

RRDY

TRDY

TMT

TOE

ROE

3

control

R/W

SSO

IE

IRRDY

ITRDY

ITOE

IROE

4

Reserved

—

5

slaveselect

R/W Slave Select Mask

1. Bits 31 to n are undefined when n is less than 32.

2. A write operation to the

status

register clears the

ROE

,

TOE

, and

E

bits.

3. Present only in master mode.

Reading undefined bits returns an undefined value. Writing to undefined bits has no effect.

rxdata Register

A master peripheral reads received data from the

rxdata

register. When the receive shift register receives

a full n bits of data, the

status

register's

RRDY

bit is set to 1 and the data is transferred into the

rxdata

register. Reading the

rxdata

register clears the

RRDY

bit. Writing to the

rxdata

register has no effect.

New data is always transferred into the

rxdata

register, whether or not the previous data was retrieved. If

RRDY

is 1 when data is transferred into the

rxdata

register (that is, the previous data was not retrieved), a

receive-overrun error occurs and the

status

register's

ROE

bit is set to 1. In this case, the contents of

rxdata

are undefined.

txdata Register

A master peripheral writes data to be transmitted into the

txdata

register. When the

status

register's

TRDY

bit is 1, it indicates that the

txdata

register is ready for new data. The

TRDY

bit is set to 0 whenever

the

txdata

register is written. The

TRDY

bit is set to 1 after data is transferred from the

txdata

register

into the transmitter shift register, which readies the

txdata

holding register to receive new data.

A master peripheral should not write to the

txdata

register until the transmitter is ready for new data. If

TRDY

is 0 and a master peripheral writes new data to the

txdata

register, a transmit-overrun error occurs

and the

status

register's

TOE

bit is set to 1. In this case, the new data is ignored, and the content of

txdata

remains unchanged.

UG-01085

2014.24.07

Register Map

10-9

SPI Core

Altera Corporation