Altera Embedded Peripherals IP User Manual

Page 145

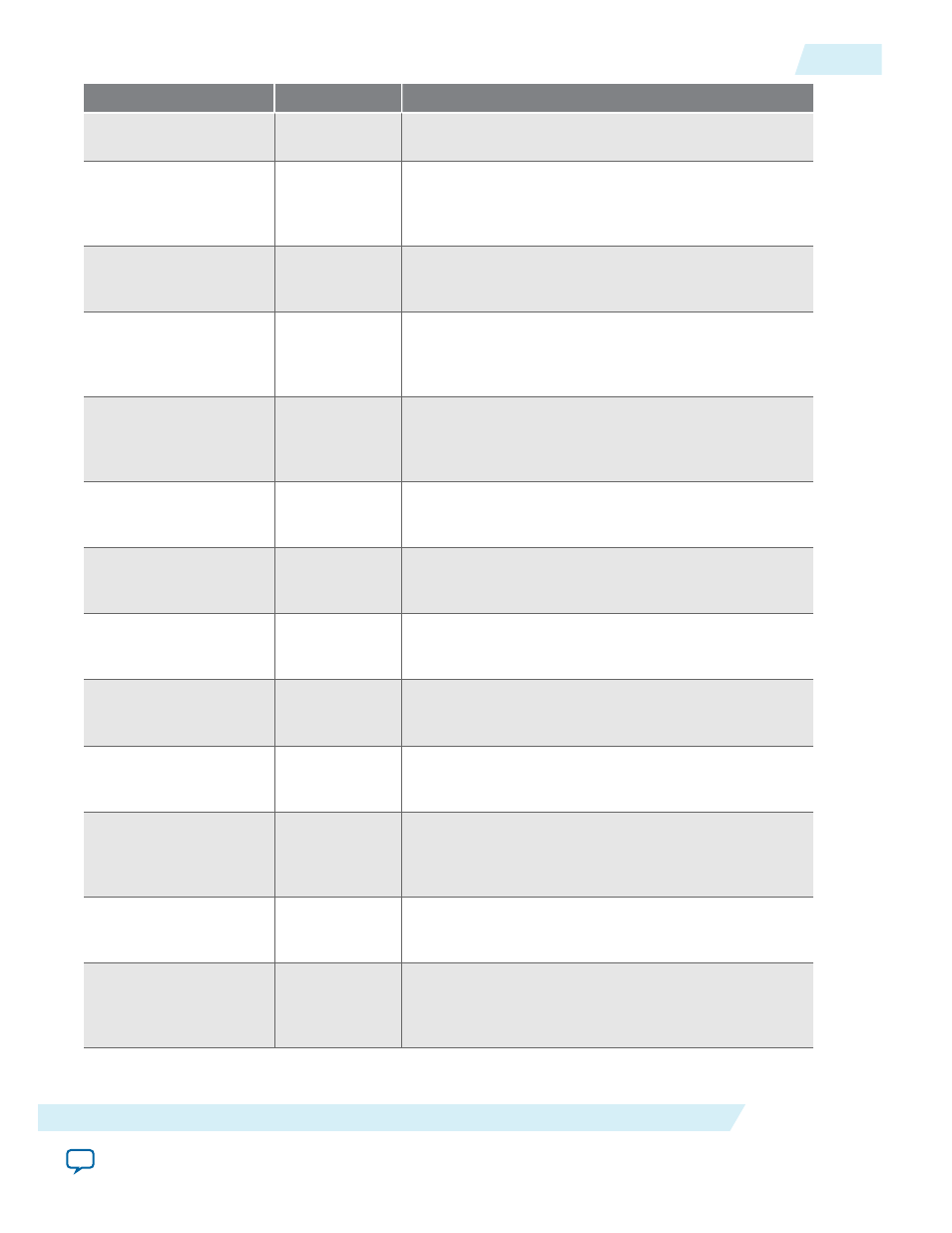

Parameters

Legal Values

Description

Size of Address Pages 12–27

The supported address size (in bits) that can be

assigned to each map number entries.

Prefetchable BAR

On or Off

Turning this option On invokes a Prefetchable Master

(PM) Bar in the PCI system. This option allows PCI-

Avalon Bridge Lite to accept and process PM transac‐

tions.

Prefetchable BAR

Size

10–31

The allowed reserved address range supported by the

PM BAR. The reserved memory space is 1 KByte (10

bits) to 4 GBytes (31 bits).

Prefetchable BAR

Avalon Address

Translation Offset

translation value> The direct translation of the value that hits the BAR and modified to a fixed address in the Avalon space. Refer to the PCI-to-Avalon Address Translation section. Non-Prefetchable BAR On or Off Turning this option On invokes a Non-Prefetchable Master (NPM) Bar in the PCI system. This option allows the PCI-Avalon Bridge Lite to accept and process NPM transactions. Non-Prefetchable BAR Size 10–31 Specifies the allowed reserved address range supported by the NPM BAR. The reserved memory space is 1 KByte (10 bits) to 4 GBytes (31 bits). Non-Prefetchable BAR Avalon Address Translation Offset translation value> The direct translation of the value that hits the BAR and modified to a fixed address in the Avalon space. Refer to PCI-to-Avalon Address Translation. I/O BAR On or Off Turning this option On enables an I/O BAR in the system. This option allows PCI-Avalon Bridge Lite to accept and process I/O type transactions. I/O BAR Size 2–8 The allowed reserved address range supported by the I/O BAR. The reserved memory space is 4 bytes (2 bits) to 256 bytes (8 bits). I/O BAR Avalon Address Translation Offset translation value> The direct translation of the value that hits the BAR and modified to a fixed address in the Avalon address space. Refer to PCI-to-Avalon Address Translation. Maximum Target Read Burst Size 1, 2, 4, 8, 16, 32, 64, or 128 Specifies the maximum FIFO depth that is used for reading. Larger values allow more reads to be read in a single transaction but also require more time to clear the FIFO content. Device ID imal value that sets the device ID register in the configuration space. Vendor ID only register that identifies the manufacturer of the device. The value of this register is assigned by the PCI Special Interest Group (SIG). UG-01085 2014.24.07 Configuration 14-11 PCI Lite Core Altera Corporation