Status register, Control register – Altera Embedded Peripherals IP User Manual

Page 116

As an example, assume that the SPI core is idle (that is, the

txdata

register and transmit shift register are

empty), when a CPU writes a data value into the

txdata

holding register. The

TRDY

bit is set to 0

momentarily, but after the data in

txdata

is transferred into the transmitter shift register,

TRDY

returns to

1. The CPU writes a second data value into the

txdata

register, and again the

TRDY

bit is set to 0. This

time the shift register is still busy transferring the original data value, so the

TRDY

bit remains at 0 until the

shift operation completes. When the operation completes, the second data value is transferred into the

transmitter shift register and the

TRDY

bit is again set to 1.

status Register

The

status

register consists of bits that indicate status conditions in the SPI core. Each bit is associated

with a corresponding interrupt-enable bit in the

control

register, as discussed in the Control Register

section. A master peripheral can read

status

at any time without changing the value of any bits. Writing

status

does clear the

ROE

,

TOE

and

E

bits.

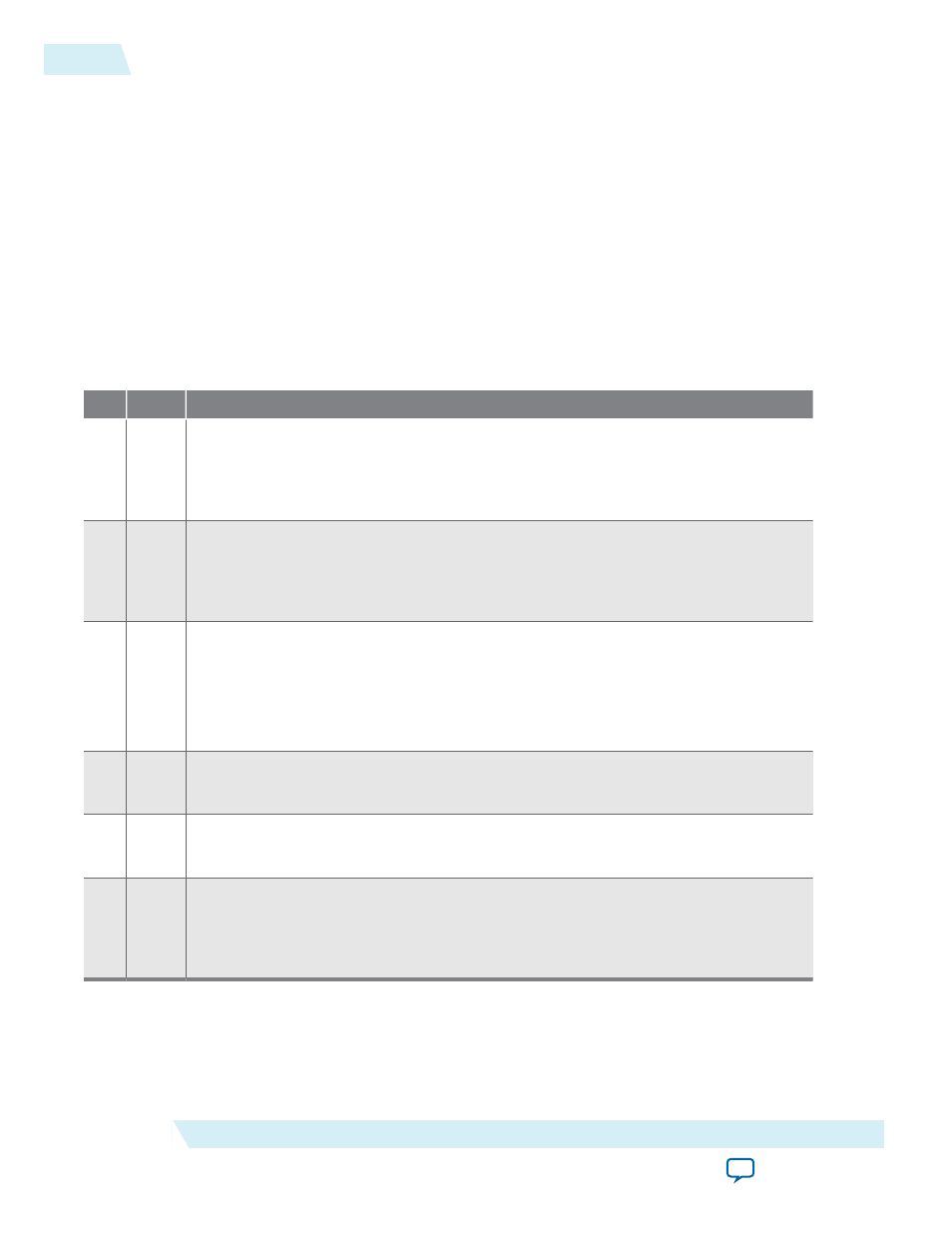

Table 10-6: status Register Bits

#

Name

Description

3

ROE

Receive-overrun error

The

ROE

bit is set to 1 if new data is received while the

rxdata

register is full (that is,

while the

RRDY

bit is 1). In this case, the new data overwrites the old. Writing to the

status

register clears the

ROE

bit to 0.

4

TOE

Transmitter-overrun error

The

TOE

bit is set to 1 if new data is written to the

txdata

register while it is still full

(that is, while the

TRDY

bit is 0). In this case, the new data is ignored. Writing to the

status

register clears the

TOE

bit to 0.

5

TMT

Transmitter shift-register empty

In master mode, the

TMT

bit is set to 0 when a transaction is in progress and set to 1

when the shift register is empty.

In slave mode, the

TMT

bit is set to 0 when the slave is selected (

SS_n

is low) or when

the SPI Slave register interface is not ready to receive data.

6

TRDY

Transmitter ready

The

TRDY

bit is set to 1 when the

txdata

register is empty.

7

RRDY

Receiver ready

The

RRDY

bit is set to 1 when the

rxdata

register is full.

8

E

Error

The

E

bit is the logical OR of the

TOE

and

ROE

bits. This is a convenience for the

programmer to detect error conditions. Writing to the

status

register clears the

E

bit

to 0.

control Register

The

control

register consists of data bits to control the SPI core's operation. A master peripheral can read

control

at any time without changing the value of any bits.

10-10

status Register

UG-01085

2014.24.07

Altera Corporation

SPI Core