Component gui – Altera Embedded Peripherals IP User Manual

Page 222

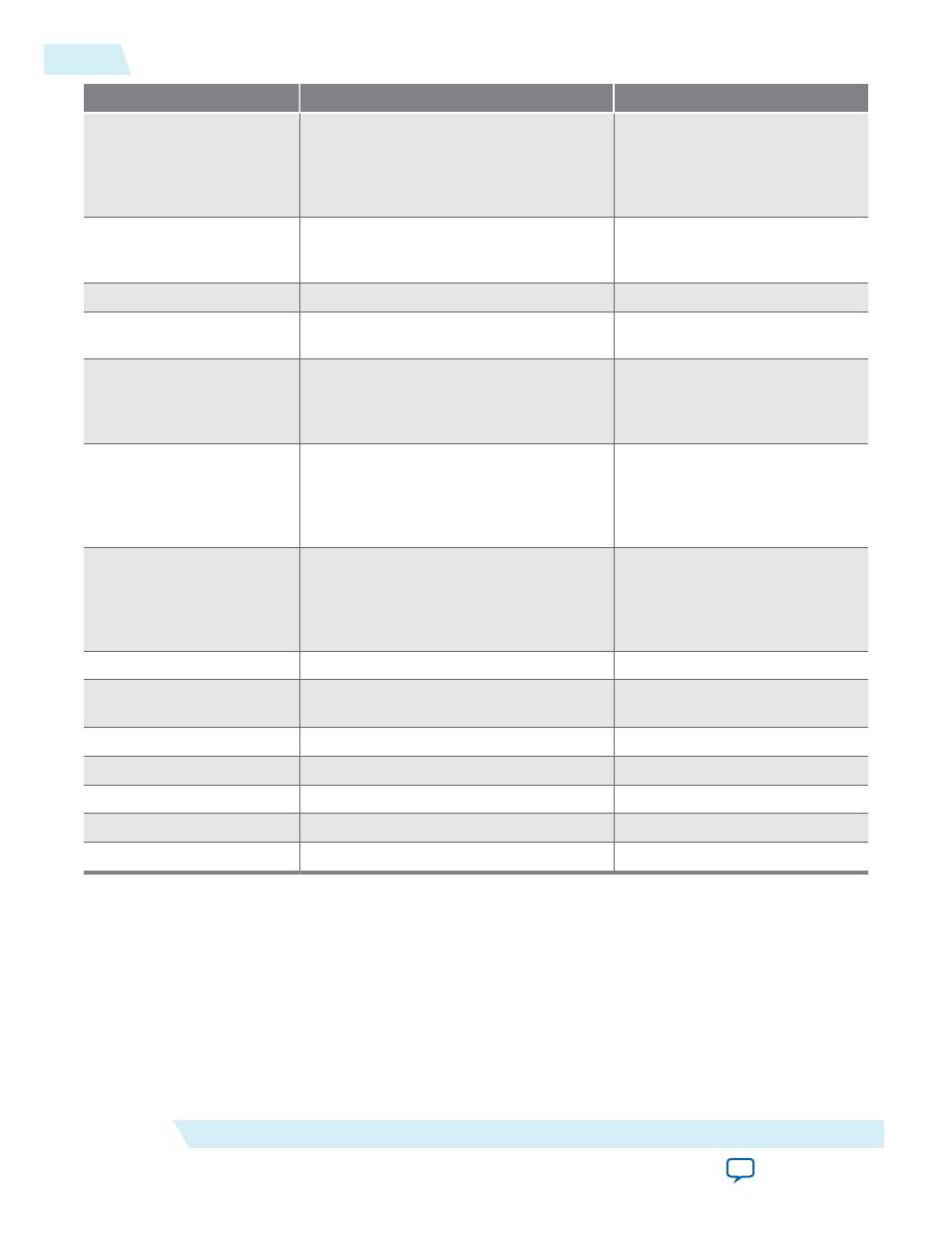

Parameter Name

Description

Allowable Range

Maximum Transfer Legth Maximum transfer length. With shorter

length width being configured, the faster

frequency of mSGDMA can operate in

FPGA.

1KB, 2KB, 4KB, 8KB, 16KB,

32KB, 64KB, 128KB,256KB,

512KB, 1MB, 2MB, 4MB, 8MB,

16MB, 32MB, 64MB, 128MB,

256MB, 512MB, 1GB, 2GB

Transfer Type

Supported transaction type

Full Word Accesses Only,

Aligned Accesses, Unaligned

Accesses

Burst Enable

Enable burst transfer

Enable, Disable

Maximum Burst Count

Maximum burst count

2, 4, 8, 16, 32, 64, 128, 256, 512,

1024

Force Burst Alignment

Enable

Disable force burst aligment. Force burst

alignment forces the masters to post bursts

of length 1 until the address is aligned to a

burst boundary.

Enable, Disable

Enable Extended Feature

Support

Enable extended features. In order to use

stride addressing, programmable burst

lengths, 64-bit addressing, or descriptor

tagging the enhanced features support must

be enabled.

Enable, Disable

Stride Addressing Enable Enable stride addressing. Stride addressing

allows the DMA to read or write data that is

interleaved in memory. Stride addressing

cannot be enabled if the burst transfer

option is enabled.

Enable, Disable

Maximum Stride Words

Maximum stride amount (in words)

1 – 2G

Programmable Burst

Enable

Enable dynamic burst programming

Enable, Disable

Packet Support Enable

Enable packetized transfer

Enable, Disable

Error Enable

Enable error field of ST interface

Enable, Disable

Error Width

Error field width

1, 2, 3, 4, 5, 6, 7, 8

Channel Enable

Enable channel field of ST interface

Enable, Disable

Channel Width

Channel field width

1, 2, 3, 4, 5, 6, 7, 8

Component GUI

22-6

Component GUI

UG-01085

2014.24.07

Altera Corporation

Altera Modular Scatter-Gather DMA