Avalon-st sink to avalon-st source, Avalon-mm write slave to avalon-st source, Avalon-st sink to avalon-st source -2 – Altera Embedded Peripherals IP User Manual

Page 157: Avalon-mm write slave to avalon-st source -2, If allow backpressure is turned on, the, Signal is asserted whenever the, Master tries to write to a full fifo buffer

If Allow backpressure is turned on, the

waitrequest

signal is asserted whenever the

data_in

master tries

to write to a full FIFO buffer.

waitrequest

is only deasserted when there is enough space in the FIFO

buffer for a new transaction to complete.

waitrequest

is asserted for read operations when there is no

data to be read from the FIFO buffer, and is deasserted when the FIFO buffer has data.

Figure 16-1: FIFO with Avalon-MM Input and Output Interfaces

S

Ava lon-MM S la ve Po rt

On-Chip FIFO

Memory

S

S

S

S

Wr

Rd

Input S ta tus I/F

(optiona l)

Out put S tatu s I/F

(opt iona l)

s ys te m inte rconne ct fab ric

Inpu t dat a

Outpu t dat a

Avalon-ST Sink to Avalon-ST Source

This configuration has streaming input and output interfaces as illustrated in the figure below. You can

parameterize most aspects of the Avalon-ST interfaces including the bits per symbol, symbols per beat,

and the width of

error

and

channel

signals. The input and output interfaces must be the same width. If

Allow backpressure is turned on, both interfaces use the

ready

and

valid

signals to indicate when space

is available in the FIFO core and when valid data is available.

.

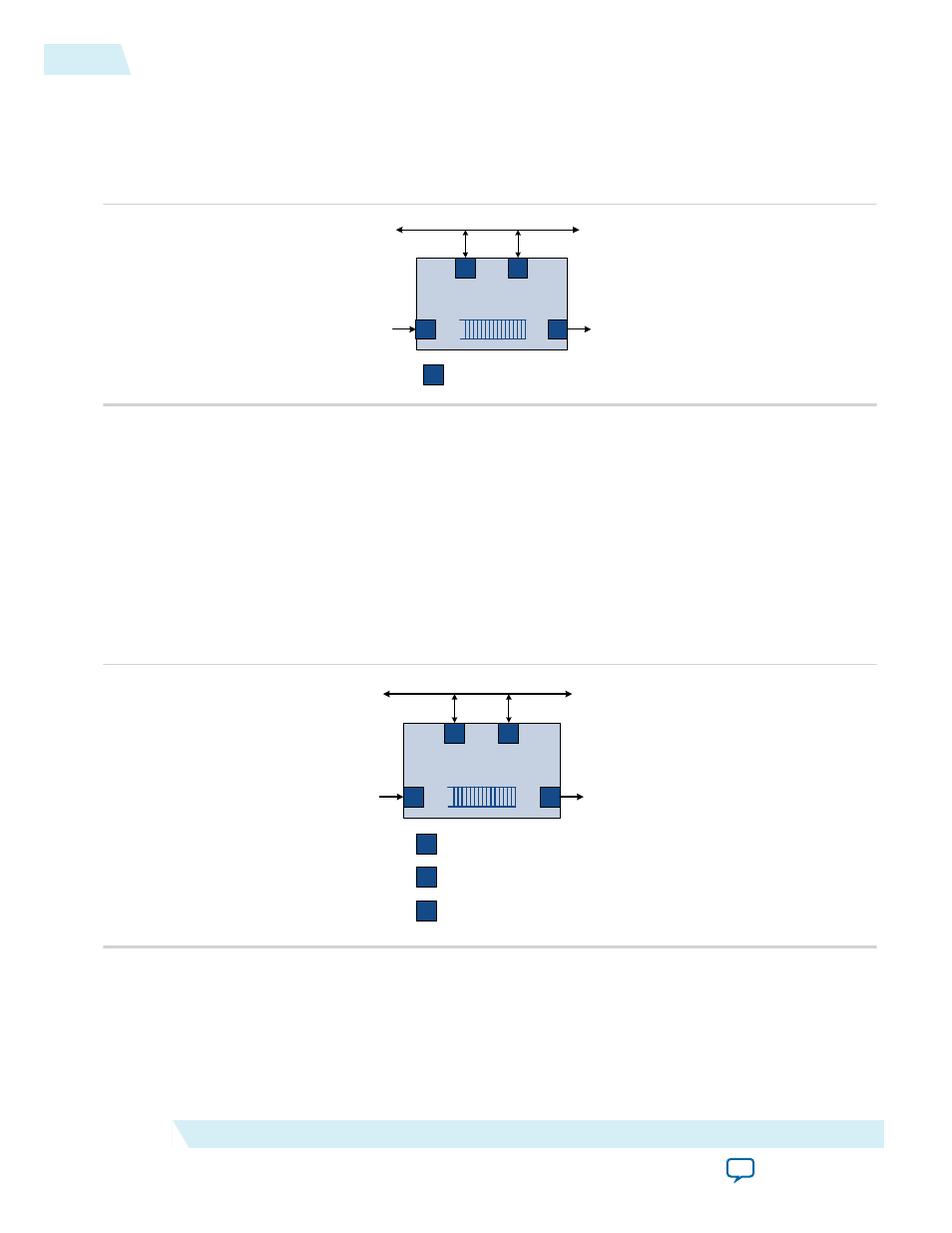

Figure 16-2: FIFO with Avalon-ST Input and Output Interfaces

S NK

Ava lon-ST S ink

On -Chip FIFO

Me mory

S

S

SN K

S RC

Input S tatu s I/F

(opt iona l)

Output S tatu s I/F

(optiona l)

S ys te m Inte rconn e ct Fab ric

St re a ming

Out put Dat a

S RC

Ava lon-ST Sou rce

S

Ava lon-MM S la ve P ort

Avalon-MM Write Slave to Avalon-ST Source

In this configuration, the input is an Avalon-MM write slave with a width of 32 bits as shown in the FIFO

with Avalon-MM Input Interface and Avalon-ST Output Interface figure below. The Avalon-ST output

(source) data width must also be 32 bits. You can configure output interface parameters, including: bits

16-2

Avalon-ST Sink to Avalon-ST Source

UG-01085

2014.24.07

Altera Corporation

On-Chip FIFO Memory Core