System reset, Configuration, Define counters – Altera Embedded Peripherals IP User Manual

Page 303: Multiple clock domain considerations, Hardware simulation considerations, Software programming model, System reset -3, Configuration -3, Define counters -3, Multiple clock domain considerations -3

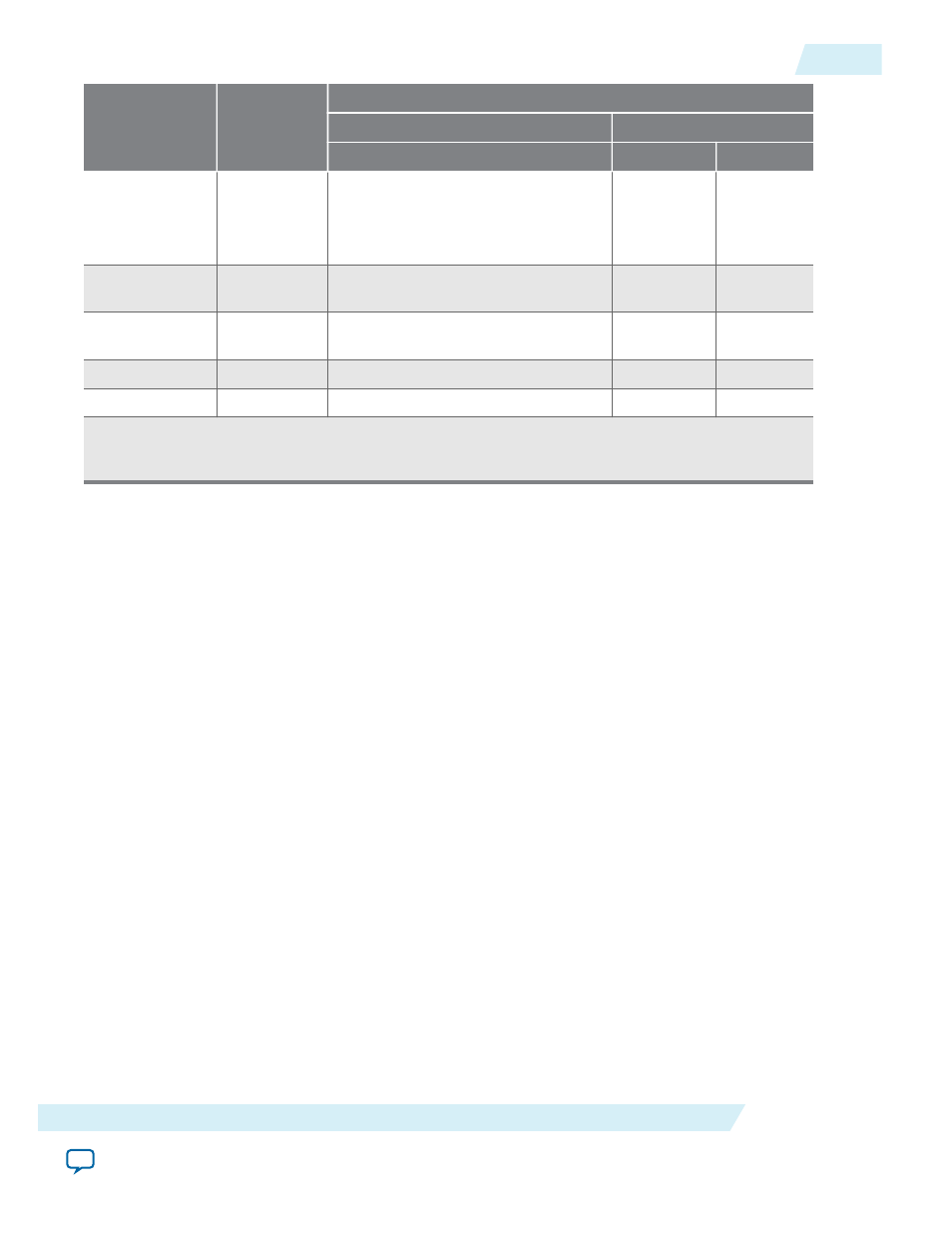

Offset

Register Name

Bit Description

Read

Write

31 ... 0

31 ... 1

0

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

4n + 0

T[n]

lo

section n clock cycle counter [31:0]

0 =

STOP

4n + 1

T[n]

hi

section n clock cycle counter [63:32]

0 =

START

4n + 2

Ev[n]

section n event counter

4n + 3

—

1. Reserved. Read values are undefined. When writing, set reserved bits to zero.

System Reset

After a system reset, the performance counter core is stopped and disabled, and all counters are set to

zero.

Configuration

The following sections list the available options in the MegaWizard

™

interface.

Define Counters

Choose the number of section counters you want to generate by selecting from the Number of

simultaneously-measured sections list. The performance counter core may have up to seven sections. If

you require more that seven sections, you can instantiate multiple performance counter cores.

Multiple Clock Domain Considerations

If your Qsys system uses multiple clocks, place the performance counter core in the same clock domain as

the CPU. Otherwise, it is not possible to convert cycle counts to seconds correctly.

Hardware Simulation Considerations

You can use this core in simulation with no special considerations.

Software Programming Model

The following sections describe the software programming model for the performance counter core.

UG-01085

2014.24.07

System Reset

31-3

Performance Counter Core

Altera Corporation