Idectl register, Document revision history, Document revision history -5 – Altera Embedded Peripherals IP User Manual

Page 45

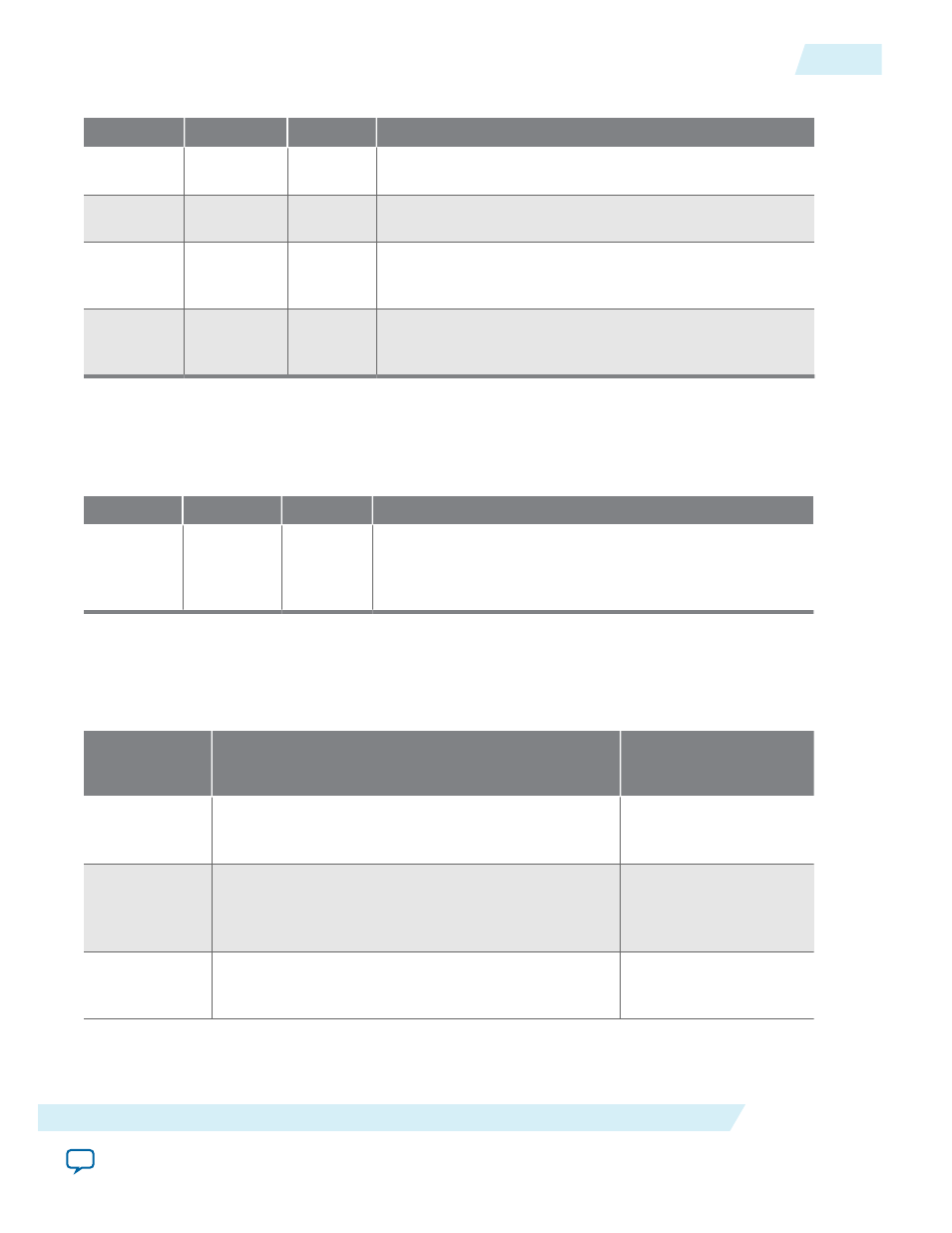

Table 4-4: cfctl Register Bits

Bit Number

Bit Name

Read/Write

Description

0

DET

RO

Detect. This bit is set to 1 when the core detects a

CompactFlash device.

1

PWR

RW

Power. When this bit is set to 1, power is being supplied to

the CompactFlash device.

2

RST

RW

Reset. When this bit is set to 1, the CompactFlash device is

held in a reset state. Setting this bit to 0 returns the device

to its active state.

3

IDET

RW

Detect Interrupt Enable. When this bit is set to 1, the

CompactFlash core generates an interrupt each time the

value of the

det

bit changes.

idectl Register

The

idectl

register controls the interface to the CompactFlash device.

Table 4-5: idectl Register

Bit Number

Bit Name

Read/Write

Description

0

IIDE

RW

IDE Interrupt Enable. When this bit is set to 1, the

CompactFlash core generates an interrupt following an

interrupt generated by the CompactFlash device. Setting

this bit to 0 disables the IDE interrupt.

Document Revision History

Table 4-6: Document Revision History

Date and

Document

Version

Changes Made

Summary of Changes

July 2014

v14.0

-Removed metion of SOPC Builder, updated to Qsys

Maintance Release

December

2010

v10.1.0

Removed the “Device Support”, “Instantiating the Core in

SOPC Builder”, and “Referenced Documents” sections.

—

July 2010

v10.0.0

No change from previous release.

—

UG-01085

2014.24.07

idectl Register

4-5

Compact Flash Core

Altera Corporation