Reserved – Altera Embedded Peripherals IP User Manual

Page 238

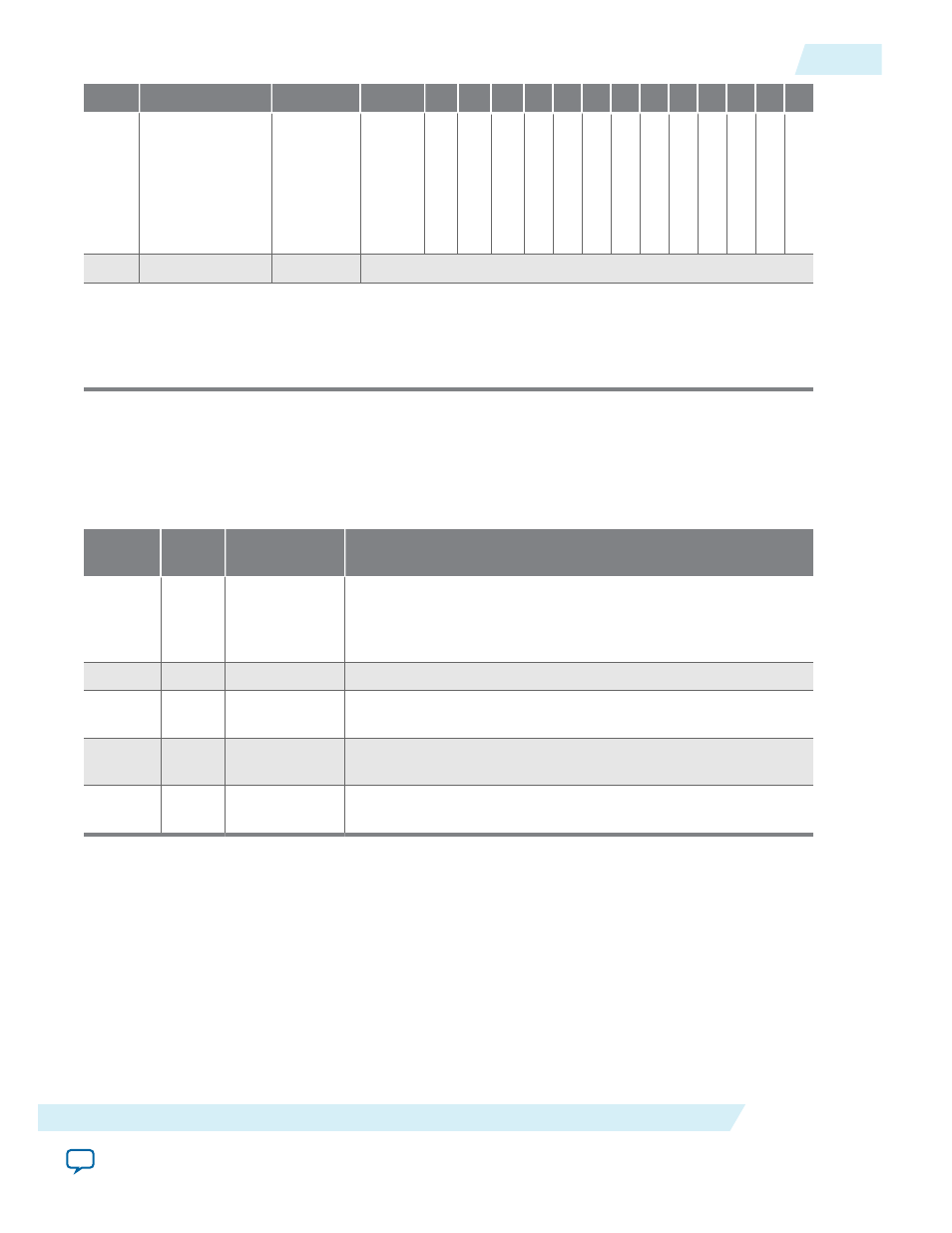

Offset

Register Name

Read/Write

31 13

12 11 10 9

8

7

6

5

4

3

2

1

0

6

control

RW

SO

FT

WA

RE

RE

SE

T

QU

AD

WO

RD

DO

UB

LE

WO

RD

WC

ON

RC

ON

LE

EN

WE

EN

RE

EN

I_

EN

GO

WO

RD

HW

B

Y

T

E

7

—

—

1. Writing zero to the

status

register clears the

LEN

,

WEOP

,

REOP

, and

DONE

bits.

2. These bits are reserved. Read values are undefined. Write zero.

3. This register is reserved. Read values are undefined. The result of a write is undefined.

status Register

The

status

register consists of individual bits that indicate conditions inside the DMA controller. The

status

register can be read at any time. Reading the

status

register does not change its value.

Table 23-4: status Register Bits

Bit

Number

Bit

Name

Read/Write/

Clear

Description

0

DONE

R/C

A DMA transaction is complete. The

DONE

bit is set to 1 when

an end of packet condition is detected or the specified transac‐

tion length is completed. Write zero to the

status

register to

clear the

DONE

bit.

1

BUSY

R

The

BUSY

bit is 1 when a DMA transaction is in progress.

2

REOP

R

The

REOP

bit is 1 when a transaction is completed due to an

end-of-packet event on the read side.

3

WEOP

R

The

WEOP

bit is 1 when a transaction is completed due to an

end of packet event on the write side.

4

LEN

R

The

LEN

bit is set to 1 when the length register decrements to

zero.

readaddress Register

The

readaddress

register specifies the first location to be read in a DMA transaction. The

readaddress

register width is determined at system generation time. It is wide enough to address the full range of all

slave ports mastered by the read port.

writeaddress Register

The

writeaddress

register specifies the first location to be written in a DMA transaction. The

writead-

dress

register width is determined at system generation time. It is wide enough to address the full range

of all slave ports mastered by the write port.

UG-01085

2014.24.07

Register Map

23-7

DMA Controller Core

Altera Corporation