Counter size, Hardware options, Counter size -3 – Altera Embedded Peripherals IP User Manual

Page 251: Hardware options -3

example, if the associated system clock has a frequency of 30 ns, and the specified Timeout Period value

is 1 µs, the true timeout period will be 1.020 microseconds.

Counter Size

The Counter Size setting determines the timer's width, which can be set to either 32 or 64 bits. A 32-bit

timer has two 16-bit period registers, whereas a 64-bit timer has four 16-bit period registers. This option

applies to the snap registers as well.

Hardware Options

The following options affect the hardware structure of the interval timer core. As a convenience, the

Preset Configurations list offers several pre-defined hardware configurations, such as:

• Simple periodic interrupt—This configuration is useful for systems that require only a periodic IRQ

generator. The period is fixed and the timer cannot be stopped, but the IRQ can be disabled.

• Full-featured—This configuration is useful for embedded processor systems that require a timer with

variable period that can be started and stopped under processor control.

• Watchdog—This configuration is useful for systems that require watchdog timer to reset the system in

the event that the system has stopped responding. Refer to the Configuring the Timer as a Watchdog

Timer section.

Register Options

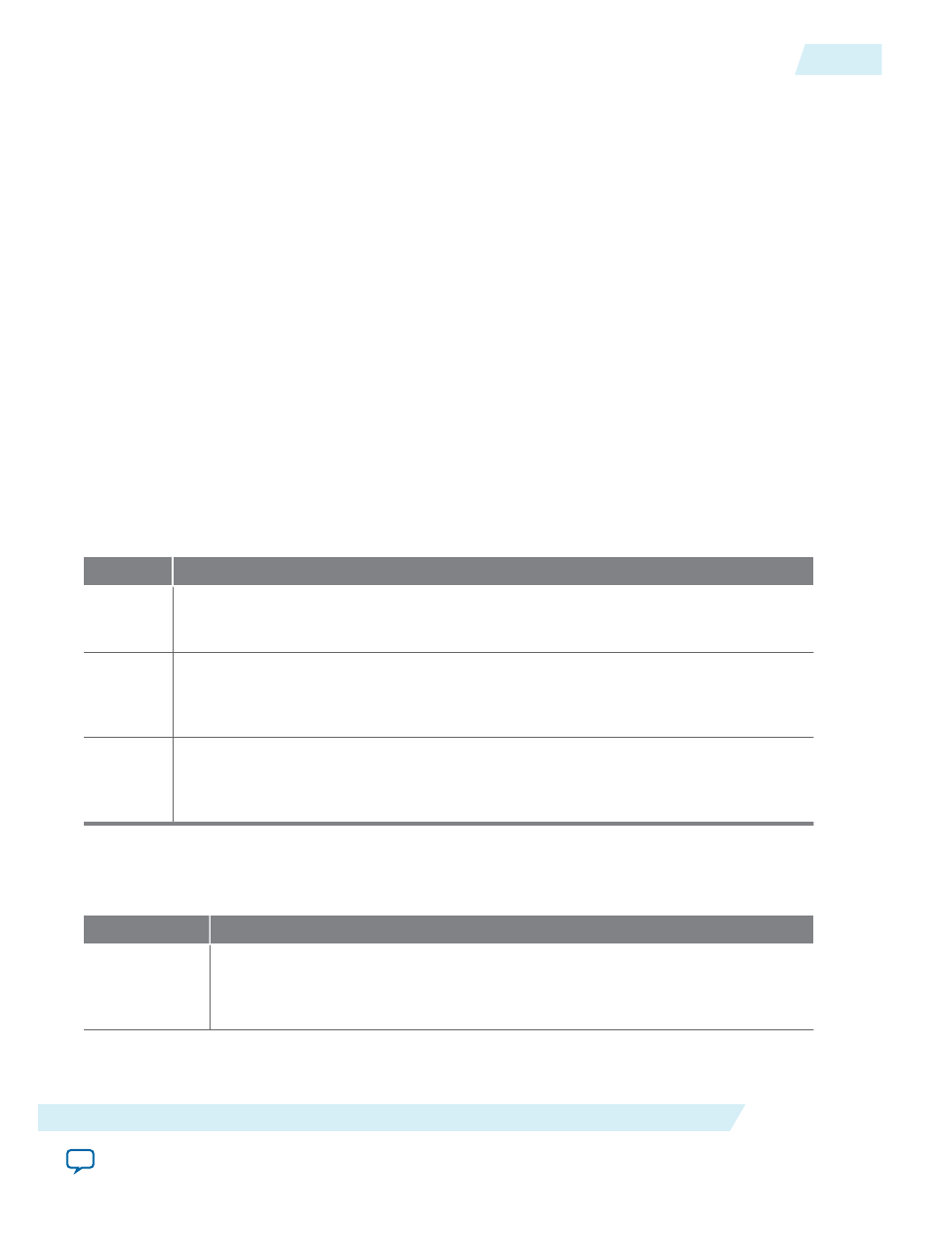

Table 25-1: Register Options

Option

Description

Writea

ble

period

When this option is enabled, a master peripheral can change the count-down period by

writing to the period registers. When disabled, the count-down period is fixed at the

specified Timeout Period, and the period registers do not exist in hardware.

Readabl

e

snapsh

ot

When this option is enabled, a master peripheral can read a snapshot of the current

count-down. When disabled, the status of the counter is detectable only via other

indicators, such as the

status

register or the IRQ signal. In this case, the snap registers

do not exist in hardware, and reading these registers produces an undefined value.

Start/

Stop

control

bits

When this option is enabled, a master peripheral can start and stop the timer by writing

the START and STOP bits in the

control

register. When disabled, the timer runs

continuously. When the System reset on timeout (watchdog) option is enabled, the

START bit is also present, regardless of the Start/Stop control bits option.

Output Signal Options

Table 25-2: Output Signal Options

Option

Description

Timeout

pulse

(1 clock

wide)

When this option is on, the core outputs a signal

timeout_pulse

. This signal

pulses high for one clock cycle whenever the timer reaches zero. When this option

is off, the

timeout_pulse

signal does not exist.

UG-01085

2014.24.07

Counter Size

25-3

Interval Timer Core

Altera Corporation