Document revision history, Document revision history -25 – Altera Embedded Peripherals IP User Manual

Page 216

Document Revision History

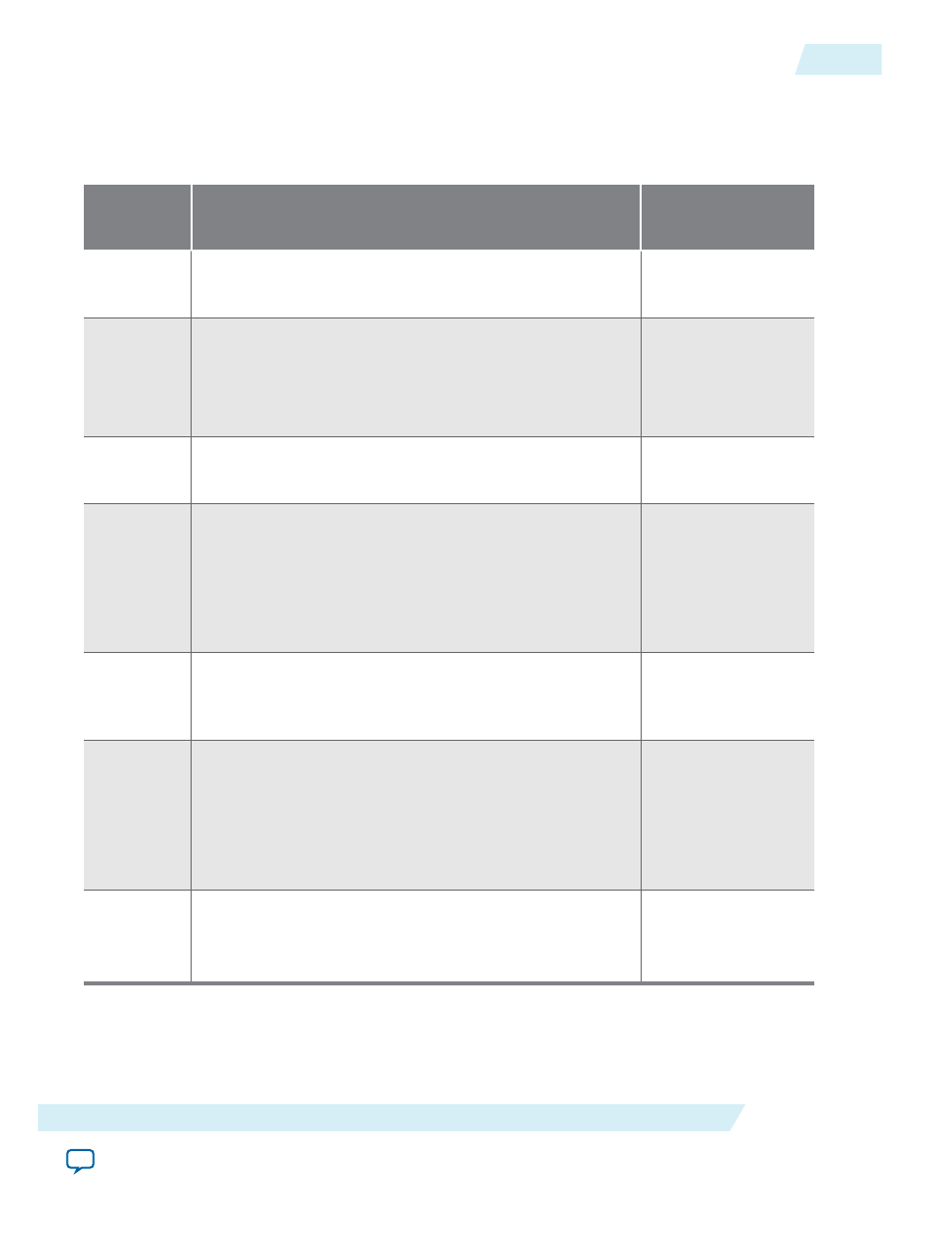

Table 21-16: Revision History

Date and

Document

Version

Changes Made

Summary of Changes

July 2014

v14.0.0

Updated Register Maps table, included version register

December

2010

v10.1.0

Updated figure 19-4 and figure 19-5.

Revised the bit description of

IE_GLOBAL

in table 19-7.

Removed the “Device Support”, “Instantiating the Core in

SOPC Builder”, and “Referenced Documents” sections.

—

July 2010

v10.0.0

No change from previous release.

—

November

2009

v9.1.0

Revised descriptions of register fields and bits.

Added description to the memory-to-stream configurations.

Added descriptions to alt_avalon_sgdma_do_sync_transfer()

and alt_avalon_sgdma_do_async_transfer() API.

Added a list on error signals implementation.

—

March

2009

v9.0.0

Added description of Enable bursting on descriptor read

master.

—

November

2008

v8.1.0

Changed to 8-1/2 x 11 page size.

Added section DMA Descriptors in Functional Specifications

Revised descriptions of register fields and bits.

Reorganized sections Software Programming Model and

Programming with SG-DMA Controller Core.

—

May 2008

v8.0.0

Added sections on burst transfers.

Updates made to

comply with the

Quartus II software

version 8.0 release.

UG-01085

2014.24.07

Document Revision History

21-25

Scatter-Gather DMA Controller Core

Altera Corporation