Altera Embedded Peripherals IP User Manual

Page 165

Bit(s)

Name

Description

5

UNDERFLOW

Is set to 1 for 1 cycle every time the FIFO underflows. The FIFO

underflows when an Avalon read master reads from an empty FIFO.

UNDERFLOW is only valid when Allow backpressure is off.

These fields are identical to those in the

status

register and are set at the same time; however, these fields

are only cleared when software writes a one to clear (W1C). The

event

fields can be used to determine if a

particular event has occurred.

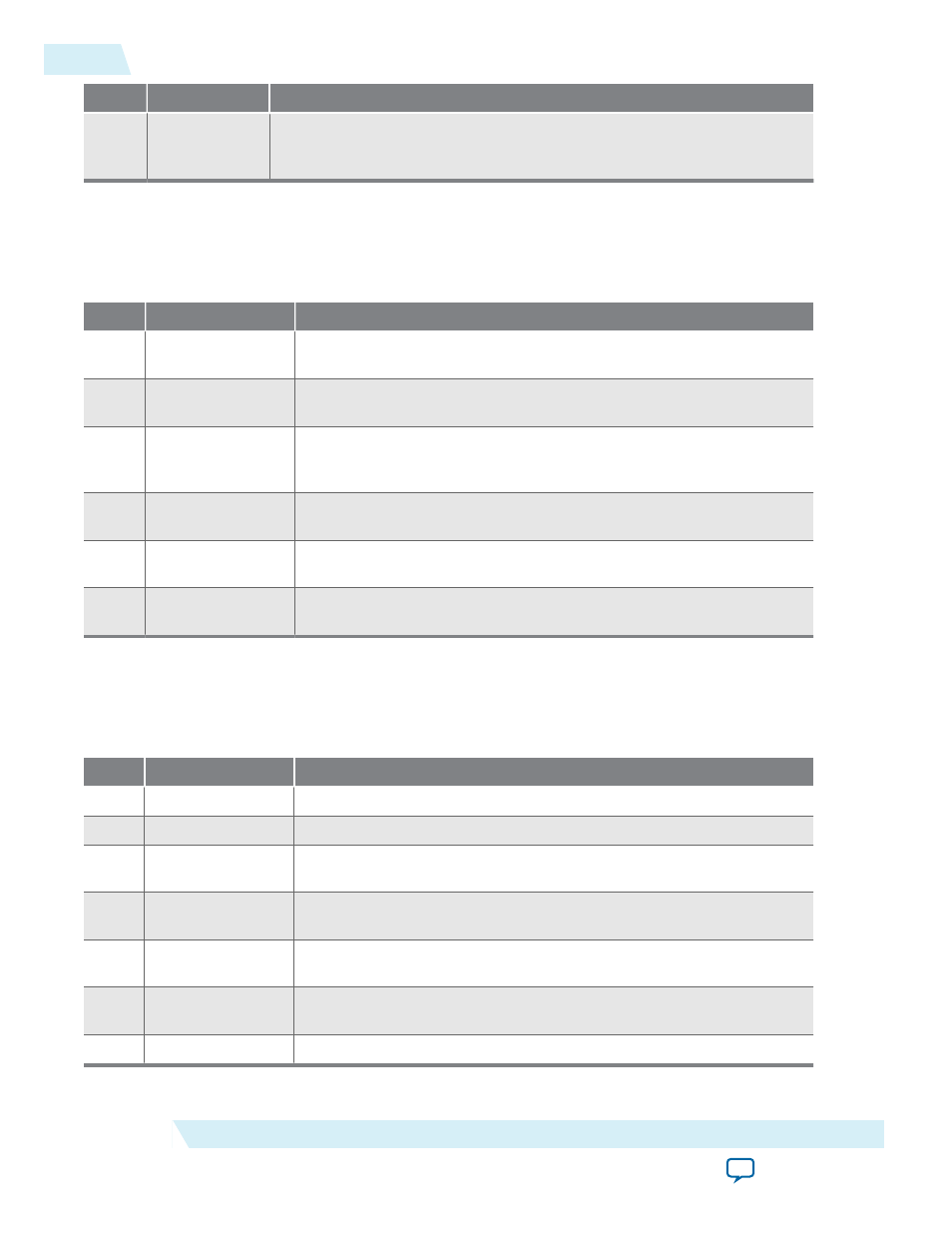

Table 16-6: Event Bit Field Descriptions

Bit(s)

Name

Description

1

E_FULL

Has a value of 1 if the FIFO has been full and the bit has not been

cleared by software.

0

E_EMPTY

Has a value of 1 if the FIFO has been empty and the bit has not been

cleared by software.

3

E_ALMOSTFULL

Has a value of 1 if the fill level of the FIFO has been greater than the

almostfull

threshold value and the bit has not been cleared by

software.

2

E_ALMOSTEMPTY

Has a value of 1 if the fill level of the FIFO has been less than the

almostempty

value and the bit has not been cleared by software.

4

E_OVERFLOW

Has a value of 1 if the FIFO has overflowed and the bit has not been

cleared by software.

5

E_UNDERFLOW

Has a value of 1 if the FIFO has underflowed and the bit has not been

cleared by software.

The table below provides a mask for the six STATUS fields. When a bit in the

event

register transitions

from a zero to a one, and the corresponding bit in the

interruptenable

register is set, the master is

interrupted.

Table 16-7: InterruptEnable Bit Field Descriptions

Bit(s)

Name

Description

1

IE_FULL

Enables an interrupt if the FIFO is currently full.

0

IE_EMPTY

Enables an interrupt if the FIFO is currently empty.

3

IE_ALMOSTFULL

Enables an interrupt if the fill level of the FIFO is greater than the

value of the

almostfull

register.

2

IE_ALMOSTEMPTY

Enables an interrupt if the fill level of the FIFO is less than the value of

the

almostempty

register.

4

IE_OVERFLOW

Enables an interrupt if the FIFO overflows. The FIFO overflows when

an Avalon write master writes to a full FIFO.

5

IE_UNDERFLOW

Enables an interrupt if the FIFO underflows. The FIFO underflows

when an Avalon read master reads from an empty FIFO.

6

ALL

Enables all 6 status conditions to interrupt.

16-10

Software Control

UG-01085

2014.24.07

Altera Corporation

On-Chip FIFO Memory Core