Interrupt servicing process, Interrupt servicing process -2 – Altera Embedded Peripherals IP User Manual

Page 321

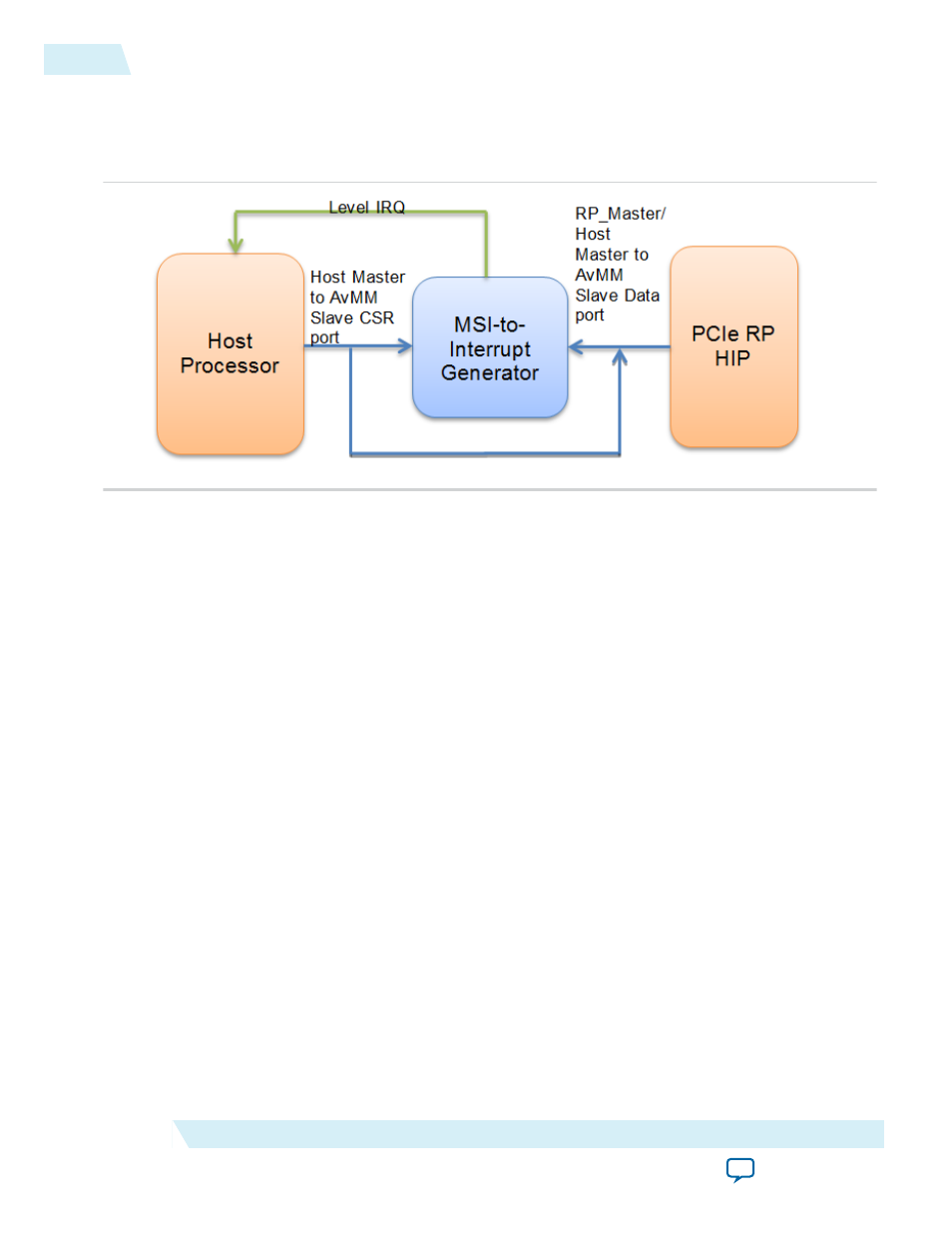

The Altera MSI-to-GIC Generator provides storage for the MSI system-specified data value. It also

generates level interrupt output when there is an unread entry. The following figure illustrates the

connection of the MSI-to-GIC Generator module in a PCIe subsystem.

Figure 33-1: MSI-to-GIC Generator in PCIe RP system

This module is connected to RP_Master of PCIe RootPort HIP issuing memory map write transaction

upon MSI TLP arrival. System-specified data value carried by the MSI TLP is written into the module

storage. The same Avalon MM Data Slave port also connects to the host processor for MSI data retrieval

upon interrupt assertion. An Altera MSI-to-GIC Generator module could contain data storage from one

to 32 words of continuous address span. Each data word of storage is associated with a corresponding

numbered bit of Status Bits and Mask Bits registers. Each data word address location can store up to 32

entries.

There is an up to 32-bit Status Register that indicates which storage word location has an unread entry.

Also, there is a similar bit size of Interrupt Mask Register that is in place to allow control of module

behavior by the host processor. The Interrupt Mask register provides flexibility for the host processor to

disregard the incoming interrupt.

The base address assigned for Altera MSI-to-GIC Generator module in the subsystem should cover the

system-specified message address of MSI capable functions during device configuration. Multiple Altera

MSI-to-GIC Generator modules could be instantiated in a subsystem to cover different system-specified

message addresses.

Avalon-MM Slave interfaces of this module honors fixed latency of access to ensure the connected master

(in this case, the RP_Master) can successfully write into the module without back pressure. This avoids

the PCIe upstream traffic from impact because of backpressuring of RP_Master.

Since MSI is multiple messages capable and multiple vectors are supported by each MSI capable function,

there is a tendency that a system-specified message address receives more than one MSI message data

before the host processor is able to service the MSI request. The Component is configurable to have each

data word address to receive up to 32 entries, before any data value is retrieved. When you reach the

maximum data value entry of 32, subsequent write transactions are dropped and logged. This ensures

every write transaction to the storage has no back pressure which may lead to system lock up.

Interrupt Servicing Process

33-2

Interrupt Servicing Process

UG-01085

2014.24.07

Altera Corporation

Altera MSI to GIC Generator