Interrupt behavior, Document revision history, Interrupt behavior -16 – Altera Embedded Peripherals IP User Manual

Page 85: Document revision history -16

The

endofpacket

register is an optional hardware feature. If the Include end-of-packet register

hardware option is not enabled, the

endofpacket

register does not exist. In this case, writing

endofpacket

has no effect, and reading returns an undefined value.

Interrupt Behavior

The UART core outputs a single IRQ signal to the Avalon-MM interface, which can connect to any

master peripheral in the system, such as a Nios II processor. The master peripheral must read the

status

register to determine the cause of the interrupt.

Every interrupt condition has an associated bit in the

status

register and an interrupt-enable bit in the

control

register. When any of the interrupt conditions occur, the associated

status

bit is set to 1 and

remains set until it is explicitly acknowledged. The IRQ output is asserted when any of the status bits are

set while the corresponding interrupt-enable bit is 1. A master peripheral can acknowledge the IRQ by

clearing the

status

register.

At reset, all interrupt-enable bits are set to 0; therefore, the core cannot assert an IRQ until a master

peripheral sets one or more of the interrupt-enable bits to 1.

All possible interrupt conditions are listed with their associated status and control (interrupt-enable) bits.

Details of each interrupt condition are provided in the

status

bit descriptions.

Document Revision History

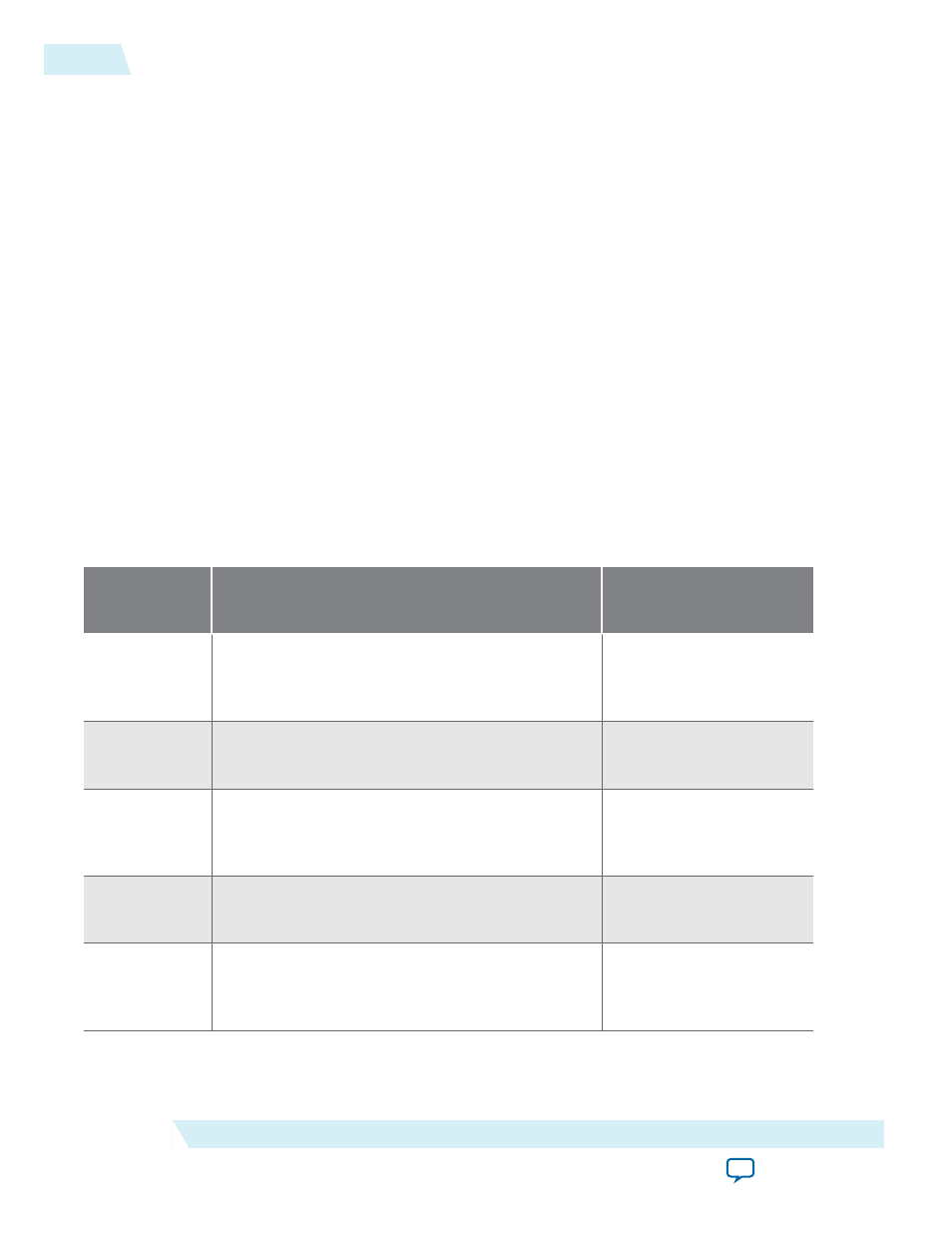

Table 8-9: Document Revision History

Date and

Document

Version

Changes Made

Summary of Changes

December

2010

v10.1.0

Removed the “Device Support”, “Instantiating the

Core in SOPC Builder”, and “Referenced Documents”

sections.

—

July 2010

v10.0.0

No change from previous release.

—

November

2009

v9.1.0

No change from previous release.

—

March 2009

v9.0.0

Added description of a new parameter, Synchronizer

stages.

—

November

2008

v8.1.0

Changed to 8-1/2 x 11 page size. No change to content. —

8-16

Interrupt Behavior

UG-01085

2014.24.07

Altera Corporation

UART Core