Software control, Software control -8 – Altera Embedded Peripherals IP User Manual

Page 163

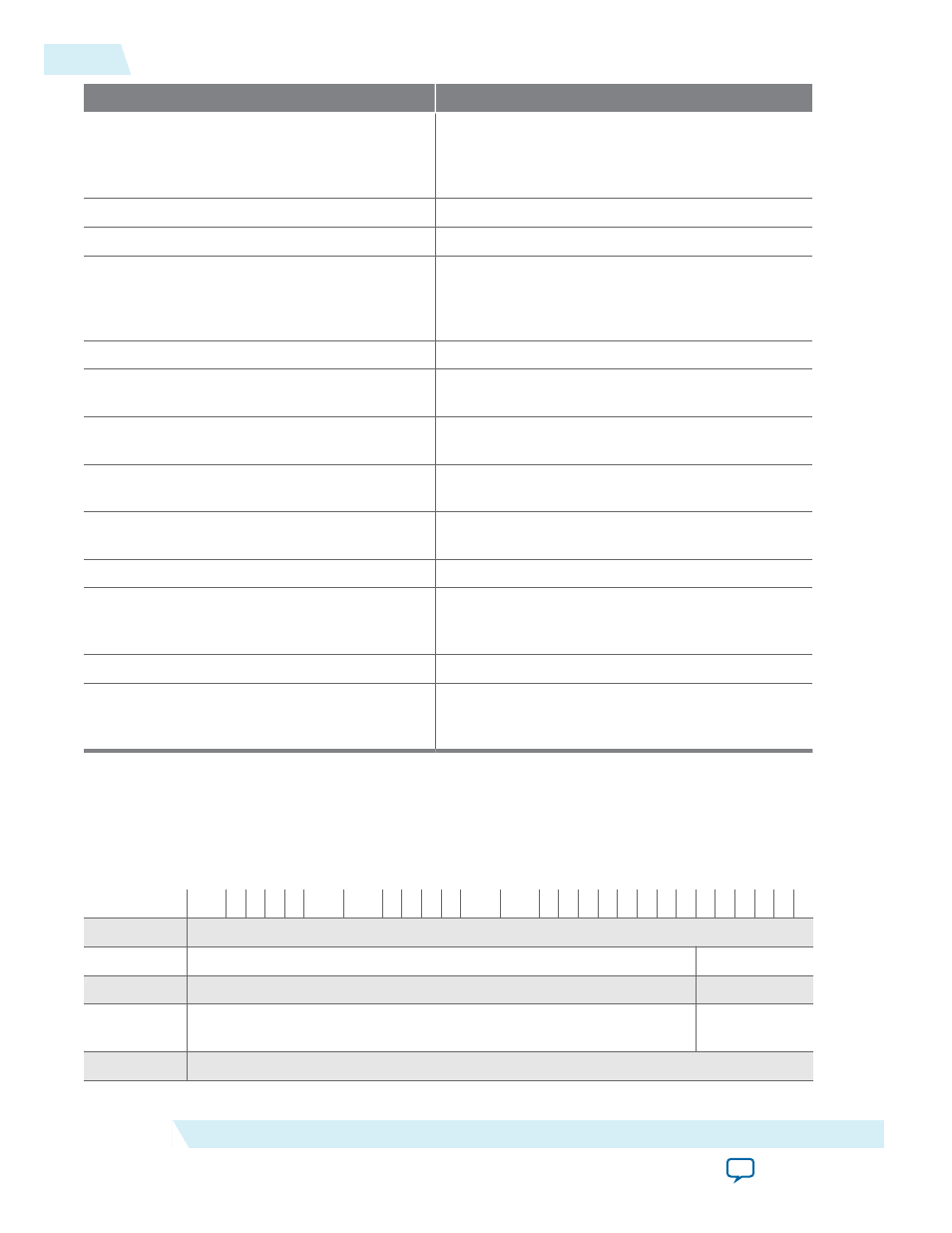

Function Name

Description

altera_avalon_fifo_read_ienable()

Returns the value of the specified bit of the

interrupt enable register. To read all of the bits at

once, use the

ALTERA_AVALON_FIFO_EVENT_ALL

mask.

altera_avalon_fifo_read_almostfull()

Returns the value of the

almostfull

register.

altera_avalon_fifo_read_almostempty()

Returns the value of the

almostempty

register.

altera_avalon_fifo_read_event()

Returns the value of the specified bit of the event

register. All of the event bits can be read at once

by using the

ALTERA_AVALON_FIFO_STATUS_ALL

mask.

altera_avalon_fifo_read_level()

Returns the fill level of the FIFO.

a

ltera_avalon_fifo_clear_event()

Clears the specified bits and the event register and

performs error checking.

altera_avalon_fifo_write_ienable()

Writes the specified bits of the

interruptenable

register and performs error checking.

altera_avalon_fifo_write_almostfull()

Writes the specified value to the

almostfull

register and performs error checking.

altera_avalon_fifo_write_

almostempty()

Writes the specified value to the

almostempty

register and performs error checking.

altera_avalon_fifo_write_fifo()

Writes the specified data to the

write_address

.

altera_avalon_fifo_write_other_info()

Writes the packet status information to the

write_address

. Only valid when the Enable

packet data option is turned on.

altera_avalon_fifo_read_fifo()

Reads data from the specified

read_address

.

altera_avalon_fifo_read__other_info()

Reads the packet status information from the

specified

read_address

. Only valid when the

Enable packet data option is turned on.

Software Control

The table below provides the register map for the

status

register. The layout of

status

register for the

input and output interfaces is identical.

Table 16-3: FIFO Status Register Memory Map

offset

31

24 23

16 15

8 7 6 5 4 3 2 1 0

base

fill_level

base + 1

i_status

base + 2

event

base + 3

interrupt

enable

base + 4

almostfull

16-8

Software Control

UG-01085

2014.24.07

Altera Corporation

On-Chip FIFO Memory Core