Functional blocks, Functional blocks -4 – Altera Embedded Peripherals IP User Manual

Page 273

The

interrupt_controller_out

and

interrupt_controller_in

interfaces have identical Avalon-ST

formats so you can daisy chain VICs together in SOPC Builder when you need more than 32 interrupts.

interrupt_controller_out

always provides valid data and cannot be back-pressured.

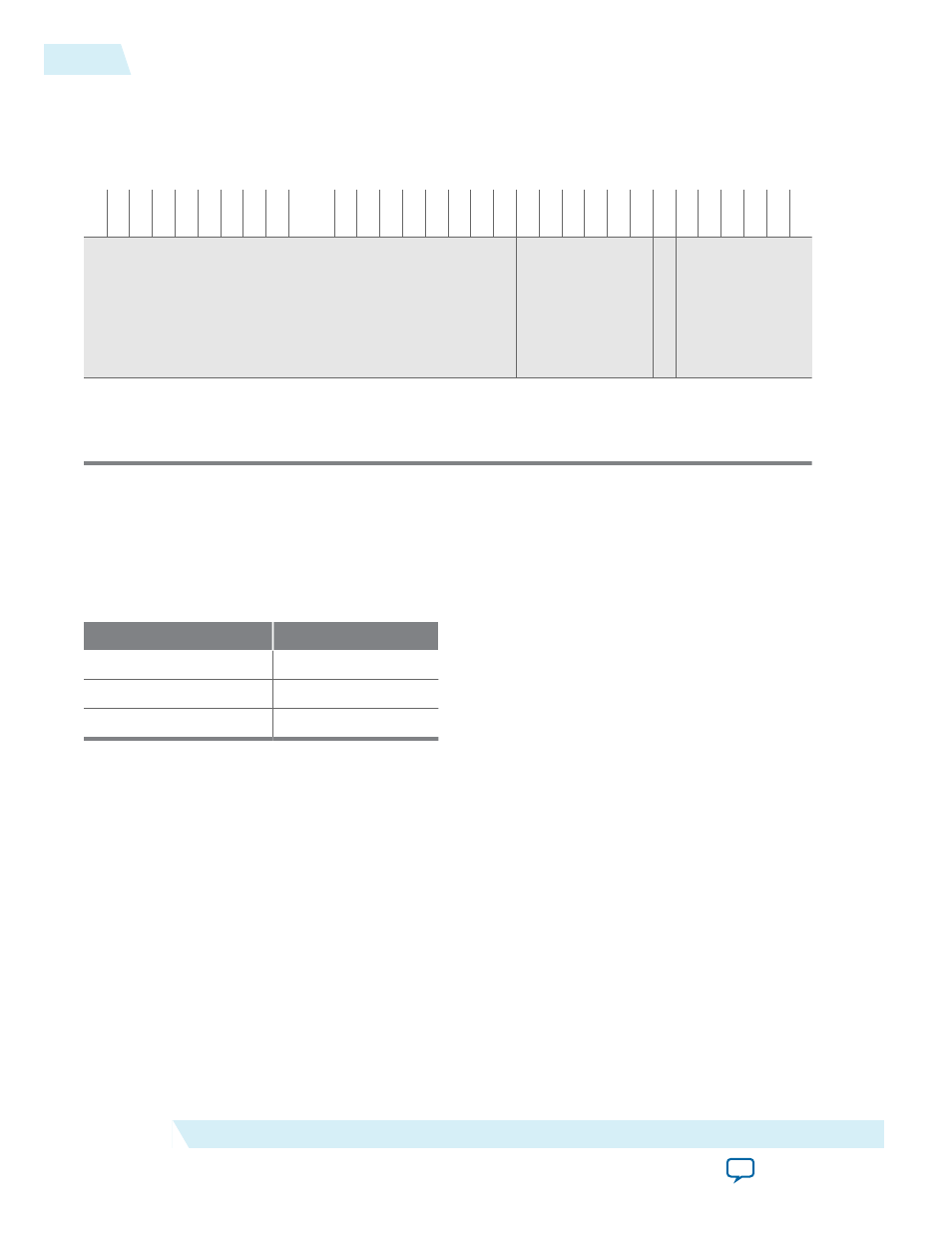

Table 28-2: VIC Avalon-ST Interface Fields

4

4

4

3

4

2

4

1

4

0

3

9

3

8

3

8

3

7

...

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0

9 8 7 6 5 4 3 2 1 0

RHA

RRS

R

N

M

I

RIL

1. RHA contains the 32-bit address of the interrupt handling routine.

2. Refer to The INT_CONFIG Register Map Table for a description of this field.

csr_access

csr_access

is a VIC CSR interface consisting of an Avalon-MM slave interface. This interface connects

to the data master of your processor. The interface’s signals are

read

,

write

,

address

,

readdata

, and

writedata

.

Table 28-3: csr_access Parameters

Parameter

Value

Read wait

1 cycle

Write wait

0 cycles

Ready latency

4 cycles

For information about the Avalon-MM slave and Avalon-ST interfaces, refer to the

Avalon Interface

Specifications

.

Functional Blocks

The following main design blocks comprise the VIC core:

• Interrupt request block

• Priority processing block

• Vector generation block

The following sections describe each functional block.

Interrupt Request Block

The interrupt request block controls the input interrupts, providing functionality such as setting interrupt

levels, setting the per-interrupt programmable registers, masking interrupts, and managing software-

controlled interrupts. You configure the number of interrupt input ports when you create the component.

Refer to Parameters section for configuration options.

28-4

Functional Blocks

UG-01085

2014.24.07

Altera Corporation

Vectored Interrupt Controller Core